CLK_ SATA 23

PC IE_CLK_VGA 12

M_ C LK _ D DR 0 9

0

SUSB#12,28,31,33,35,39,40

R260 M760SU ? ? ?

P CIE_CLK_MIN I#_R

R 278 22_04

C411 * 10P_50V _04

Z_C LK1 21

Z2307

3. 3V S

S_DA T9,10,22,33

M_ CL K_ DD R3 #

RN 2 0

4P2RX33_04

1 4

2 3

Q1 2

2N7002W

G

DS

PCIE_C LK_N B#

P CIE_CLK_NB#_R

RN2

4P2RX0_04

1 4

2 3

FB_INA

PCLK_ SB

P CIE_VGA_R #

M_CLK_DDR2

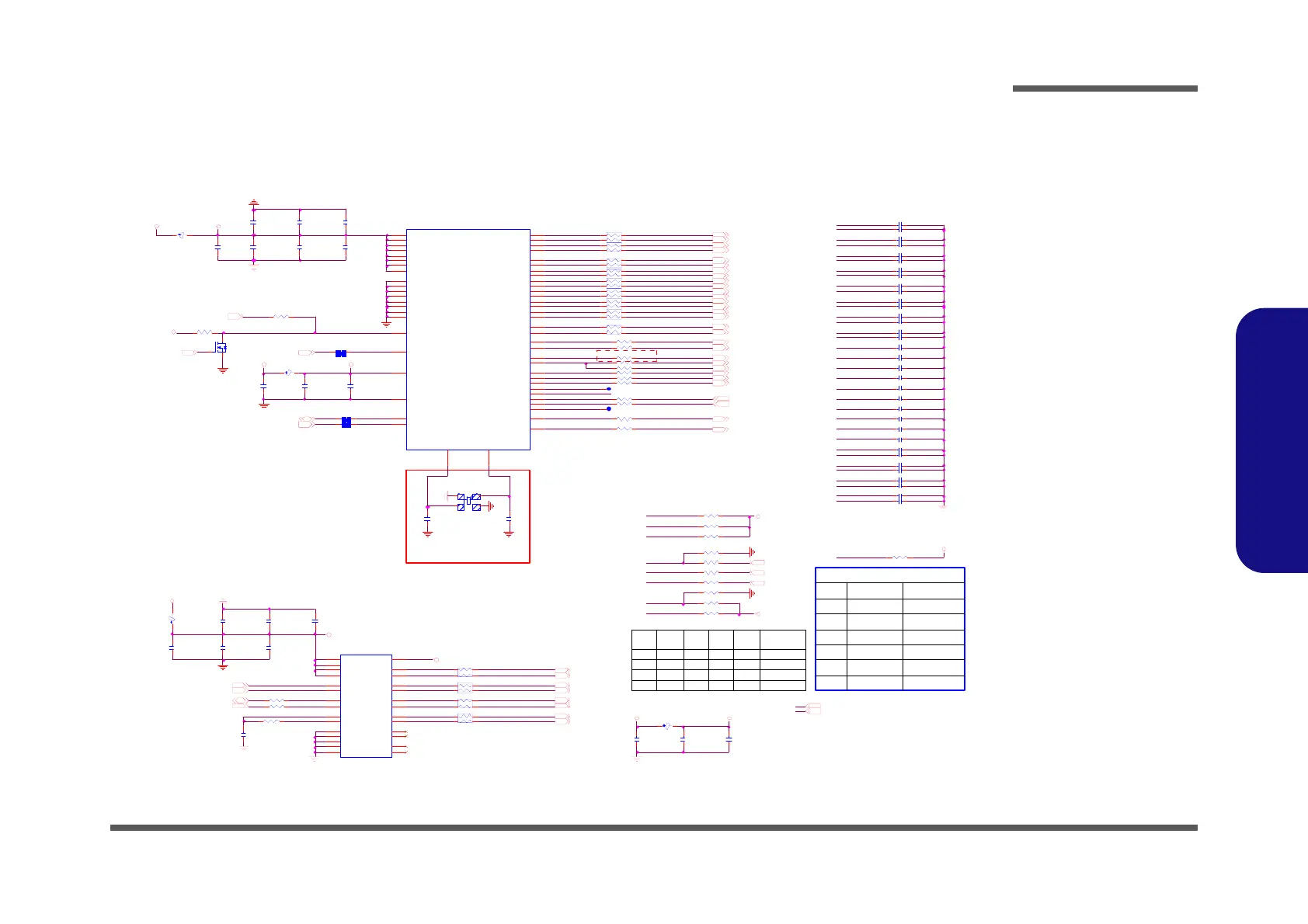

U15

IC S9P 93 5

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17 16

15

DD RC0

DDRT0

VDD 1 .8

DDRT1

DD RC1

GN D

VDD A1.8

GN D

CL K _ INT

CL K _ INC

VDD 1 .8

DDRT2

DD RC2

GN D

GN D

DD RC5

DDRT5

VDD 1 .8

GN D

DD RC4

DDRT4

VDD 1 .8

SDATA

SCLK

FB_IN

FB_OUT DDRT3

DD RC3

0

PCIE_CLK_SB 22

P CIE_CLK_NEW_R

M_ CL K_ DD R2 #

C6 7 6

33P_50V_04

C342

.1U_ 1 0V_ X7 R_ 04

Clock Generator Pin 15

Z_CLK0

M_ CL K_ DD R2

C377 * 10P_50V _04

(LO)Non-STUFF

B SEL 2

PECLKREQ1#

RN 2 1

4P2RX33_04

1 4

2 3

L68 H CB1005KF-121T20

BS EL 0

KBC _ PCLK

PCIE_C LK_M INI#

C384

.1U _10V_X7R_04

1

CLKGEN_FS L1

PCICLK6

H_ CL K_ CPU # 2

CLK_14M_968

C376

.1U _10 V_X7R _0 4

PC LK _C ARD

CL K _ 48 M _C A RD

M_CLK_DDR1#_R

C677

33P_50V_04

PCIE_CLK_SB# 22

M_CLK_DDR3#_R

STP_ PC I#

P CIE_VGA_R

C654

10U_10V_08

C349 * 10P_50V _04

M_CLK_DDR2_R

1

R 478 33_04

S_CLK9,10,22,33

Z23 05

CL K _ S ATA#

R 274 10K_04

R 481 33_04

10 0 M Hz

1.8VS

M_ C LK _ D DR 2 # 1 0

C390 * 10P_50V _04

R247 *0_04

RN4

4P2RX0_04

1 4

2 3

RESET#

M_ C LK _ D DR 2 1 0

PCIE_C LK_N B

Z_CLK0

CLK_14M_671M X 6

PCLK_ CAR D

C4 1 4

1U_10V_06

RN 1 8

4P2RX33_04

1 4

2 3

Pin 1

3.3VS

C678 * 10P_50V _04

3.3VS

CPUSTP#6

R268 *2.7K_04

Host Clock

0

CLKGEN_MODE

RN 1 1

4P2RX33_04

1 4

2 3

C LKBU F_ AVDD

CLK_48M_CARD

C404 * 10P_50V _04

PCIE_C LK_M INI

C7 22

10U_10V_08

(HI)PULLl-UP

RN 2 5

4P2RX33_04

1 4

2 3

CL K GE N_ VDD

CL K EN

M_ CL K_ DD R1 #

R4 82 1 0 K_ 04

CPU _BSEL 0 2

PCLK_SB 21

M_CLK_DDR1#

P CIE_CLK_NB_R

R 267 *10K_04

RN 2 6

4P2RX33_04

1 4

2 3

CPU _BSEL 1 2

M_ C LK _ D DR 3 # 1 0

C715

10U_10V _08

CPU_STOP#

0

PCIE_CLK_HD V 11

R262 *0_04

L66

H CB1608KF-121T25

Mobile mode

M_CLK_DDR3#

M_ CL K_ DD R1

C341 * 10P_50V _04

STP_PCI#

P CLK_D EBU G_R

Z2301

C4 0 2

.1U _ 10 V_ X 7R _ 04

PCIE_CLK_NEW # 33

0

M_CLK_DDR0

C391 * 10P_50V _04

CL K _ S ATA

Z2304

20 0 M Hz

Z_C LK0 6

PCIE_C LK_SB

C L K_SA TA_ R

R475 *1K_04

Status

Z_CLK1

C LK_12M_US B_R

RN5

4P2RX0_04

1 4

2 3

C6 6 0

10U _10V_08

PCICLK5

R261 10K_04

R494 *10m il_s hort

X3

14.318MH Z

12

34

1

M_ C LK _ D DR 1 # 9

CLK_14M_307ELV 11

C401 * 10P_50V _04

PCI_STOP#Pin 12

1

CPU _BSEL 2 2

S EL24_48#

M_ CL K_ DD R0

C3 9 8

.1U_ 1 0V_ X7 R_ 04

C400 * 10P_50V _04

C345 * 10P_50V _04

H_ CL K_ CPU #

CLK_SATA#

C L KGEN _F SL 1

PE CL KREQ 0#

R 264 2.2K _04

C424 * 10P_50V _04

3. 3 V S

H_ CL K_ NB 4

RN 1 9

4P2RX33_04

1 4

2 3

PCICLK3

1

1.8V S

CLKGEN_FS L0

CLKGEN_FS 4

M_CLK_DDR1_R

M _F W DSD CLKOA_D #5

C L K_SA TA# _ R

L33

HCB 1005K F-121T20

R 266 *10m il_short

C408 * 10P_50V _04

13 3 M Hz

C3 4 4

10P_50V _04

Place CRYSTAL Within 500

mils of ICS9LPR600

Z _C LK1_R

PE CL KREQ 1#

Z2303

R 487 10K_04

PECLKREQ1#

CLK_12M_USB

C340 * 10P_50V _04

1.8VS 4,5,6,7,11,13,14,15,17,19,21,22,23,24,35

PCIE_CLK_HD V# 11

C418 * 10P_50V _04

MINI_CARD_CLKREQ# 33

Z _C LK0_R

H _ CL K_ NB# _ R

R563 *2.7K_04

C7 0 6

1U _10V_06

M_ C LK _ D DR 1 9

PCIE_C LK_H DV

R 493 33_04

1

CLK_14M _968

C378

.1U _10 V_X7R _0 4

P CIE_CLK_SB#_R

Pin 17

CLKBU F_AV DD

C657

.1U_ 1 0V_ X7 R_ 04

M_CLK_DDR3_R

M_CLK_DDR0_R

R485 *0_04

C385 * 10P_50V _04

C407 * 10P_50V _04

NEW_CAR D_CLKR EQ# 33

M_CLK_DDR0#

C381 * 10P_50V _04

F req ue nc y

0

3.3VS

C372 * 10P_50V _04

C394 * 10P_50V _04

Mode

CLK_STOP#

PCLK_CAR D 28

H_ CL K_ CPU

M_CLK_DDR2#

C429 * 10P_50V _04

PCIE_CLK_MIN I 33

PC IE_CLK_VGA# 12

R 476 2.2K _04

0

PCIE_CLK_NB# 4

PECLKREQ0#

Z_CLK1

R 270 33_04C3 80

.01U _16V_X7R_04

C347 * 10P_50V _04

R 491 22_04

CL K _ 48 M_ C A RD 28

FB_OU TA

PCIE_C LK_SB#

H _ CL K_ CPU _R

RN3

4P2RX0_04

1 4

2 3

C3 5 6

.1U_10V _X7R_04

PCIE_CLK_NB 4

CLK_14M _671MX

M_CLK_DDR1

CLK_SATA

M_ CL K_ DD R3

R246 22_04

1

FS 3

C L KGEN _F SL 2

H_ CL K_ NB#

CL K _ 12 M _U S B

C399 * 10P_50V _04

R 260 33_04

0

R271 *0_04

C338 * 10P_50V _04

R 492 33_04

C679 * 10P_50V _04

P CIE_CLK_HD V_R

P CIE_CLK_SB_R

C L KGEN _F SL 0

FS4

M_FWDSD CLKOA_D5

S_C LK9,10,22,33

H _ CL K_ CPU #_ R

C3 5 1

.1U_10V _X7R_04

PECLKREQ0#

H_ CL K_ NB# 4

C416 * 10P_50V _04

0

CLKEN#37

PCIE_C LK_H DV#

C337 * 10P_50V _04

KBC_PC LK

CL K GE N_ MO DE

C346

.1U_ 1 0 V_X7 R_ 0 4

16 6 M Hz

S_D AT9,10,22,33

P CIE_CLK_HD V#_R

L70 HC B1608KF-121T25

P CIE_CLK_MIN I_R

CLKGEN_FS 3

C410 * 10P_50V _04

1

R 269 *10m il_short

CL K BU F_V DD

R248 *0_04

Desktop mode

R 479 2.2K _04

RN 1 7

4P2RX33_04

1 4

2 3

10

3.3V S

M_ C LK _ D DR 3 1 0

Z2302

C375 * 10P_50V _04

C705 * 10P_50V _04

C352

.1 U_ 1 0 V_ X7 R_ 0 4

H _ CL K_ NB_ R

CL K _ 12 M_ U S B 2 3

PCIE_C LK_N EW

C701 * 10P_50V _04

CLKG EN_ VDD A

CLK_14M_968 22

CLK_14M _307ELV

M_CLK_DDR2#_R

C L KGEN _F S3

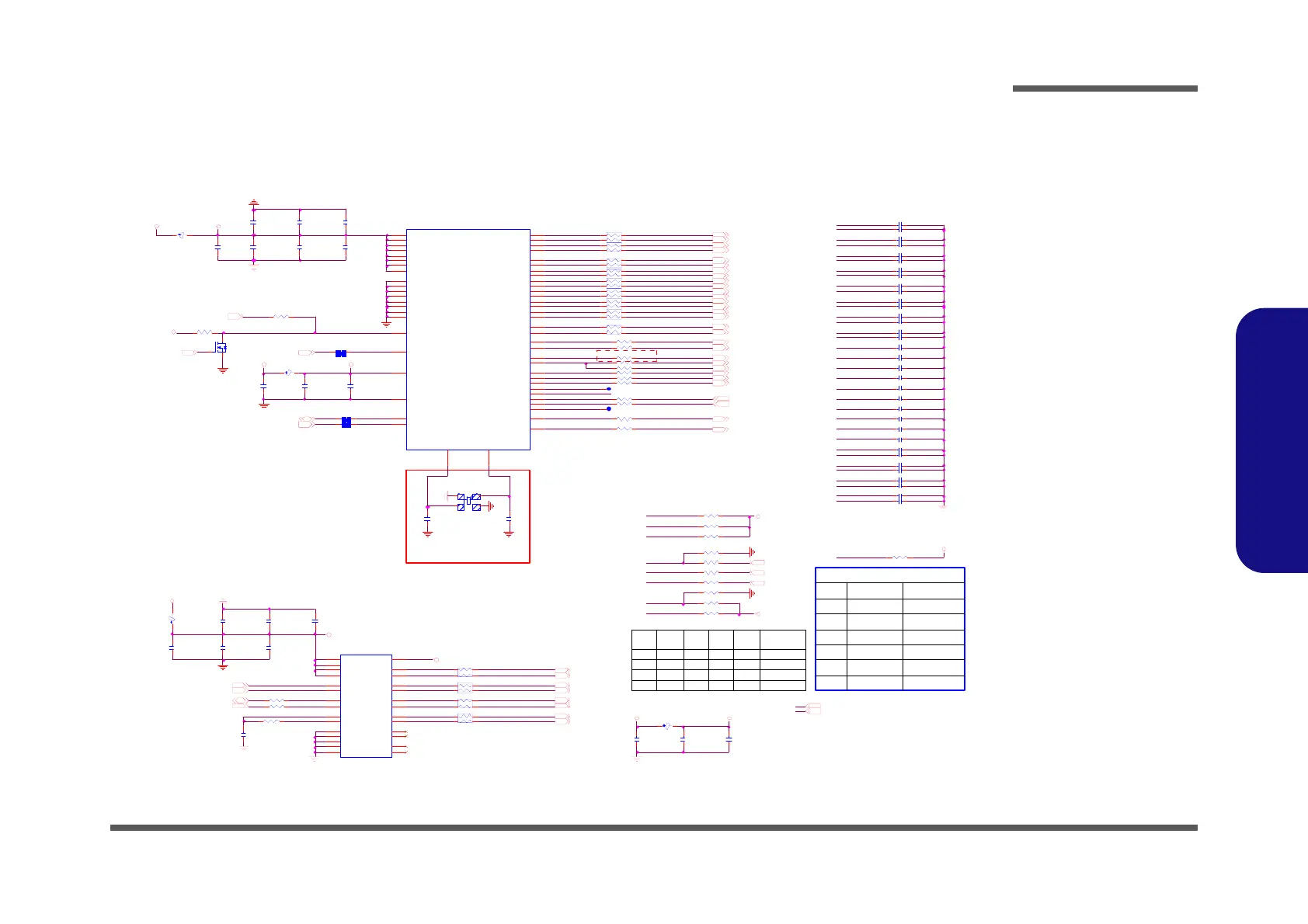

U33

ICS9LPR600CGLF

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

(CL K_ ST OP# )/V T T PW RG D/P D #

VD DREF

** FSL0/R EF0_2x

*FSL1/R EF1_2x

X1

X2

GN DR E F

GN DP C I

**FSL2/PC ICLK0_2x F

* *FS3/PC ICLK1_2xF

**F S 4/ P C I CL K 2

* (PCI_ STOP#)/PC ICLK3

GN DP C I

VD DP CI

** MO D E /P C ICL K4

(PE CLKREQ 0#)/PC ICLK5

(PE CLKREQ 1#)/PC ICLK6

PC ICLK7

VD DP CI

GN DZ

ZCLK0

ZCLK1

VD DZ

VD D48

12MHz

** SEL24_48#/24_48MHz

GN D4 8

*(C PU_ STOP#)/R ESET #

VD DCPU

CPU T _L 0 F

CPUC_L0F

GN DC P U

CPU T _L 1

CPUC_L1

VD DA

SA TAC L KT_ L

SATACL KC_L

GN DA

SC LK

SD ATA

PC IET_L 0

PCIEC _L 0

GN DP C IE X

PC IET_L 1

PCIEC _L 1

VD DP CI EX

PC IET_L 2

PCIEC _L 2

PC IET_L 3

PCIEC _L 3

PC IET_L 4 F

PCIEC_L4F

GN DP C IE X

PC IET_L 5 F

PCIEC_L5F

VD DP CI EX

RN 2 7

4P2RX33_04

1 4

2 3

Pin 28

PCIE_CLK_NEW 33

R 265 33_04

VTTOWRGD/PD#

1

H_ CL K_ NB

M_ CL K_ DD R0 #

Z2306

PCIE_C LK_N EW#

CLK_14M_671MX

PC LK _SB

P CIE_CLK_NEW#_R

M_CLK_DDR0#_R

CLK_ SATA # 2 3

H_ CL K_ CPU 2

C LK_14M_307ELV

R 480 2.7K _04

R 263 33_04

3.3VS 6,10,11,19,20,21,22,23,24,27,28,29,30,31,32,33,34,35,37

M_CLK_DDR3

KBC_PCLK 27

PCIE_CLK_MIN I# 33

C373 * 10P_50V _04

M_ C LK _ D DR 0 # 9

C L KGEN _F S4

C704 * 10P_50V _04

Pin 16

CLKGEN_FS L2

C353 * 10P_50V _04

C663

.01U_16V _X7R_04

BSEL1

Loading...

Loading...