85

DVD-3910

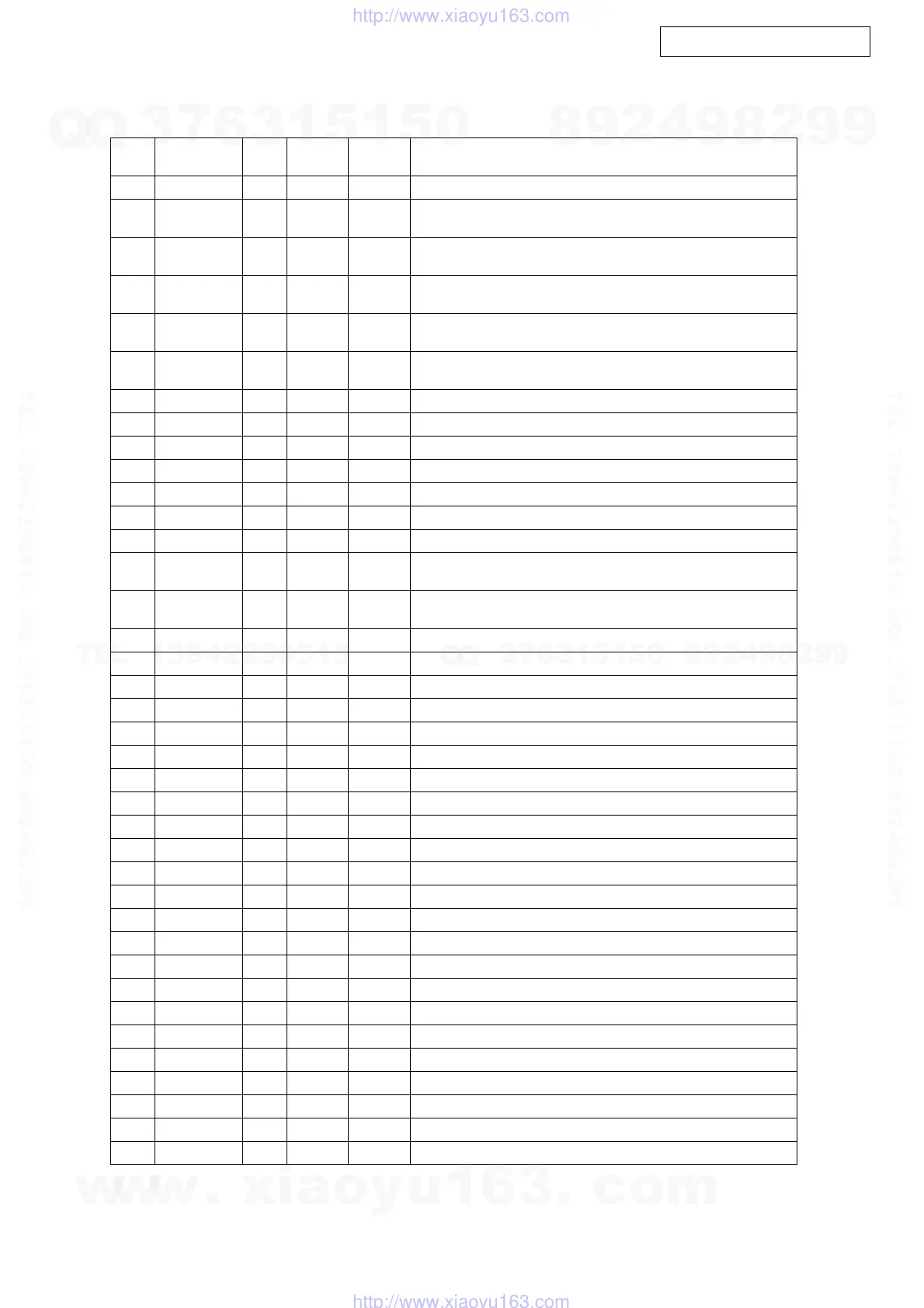

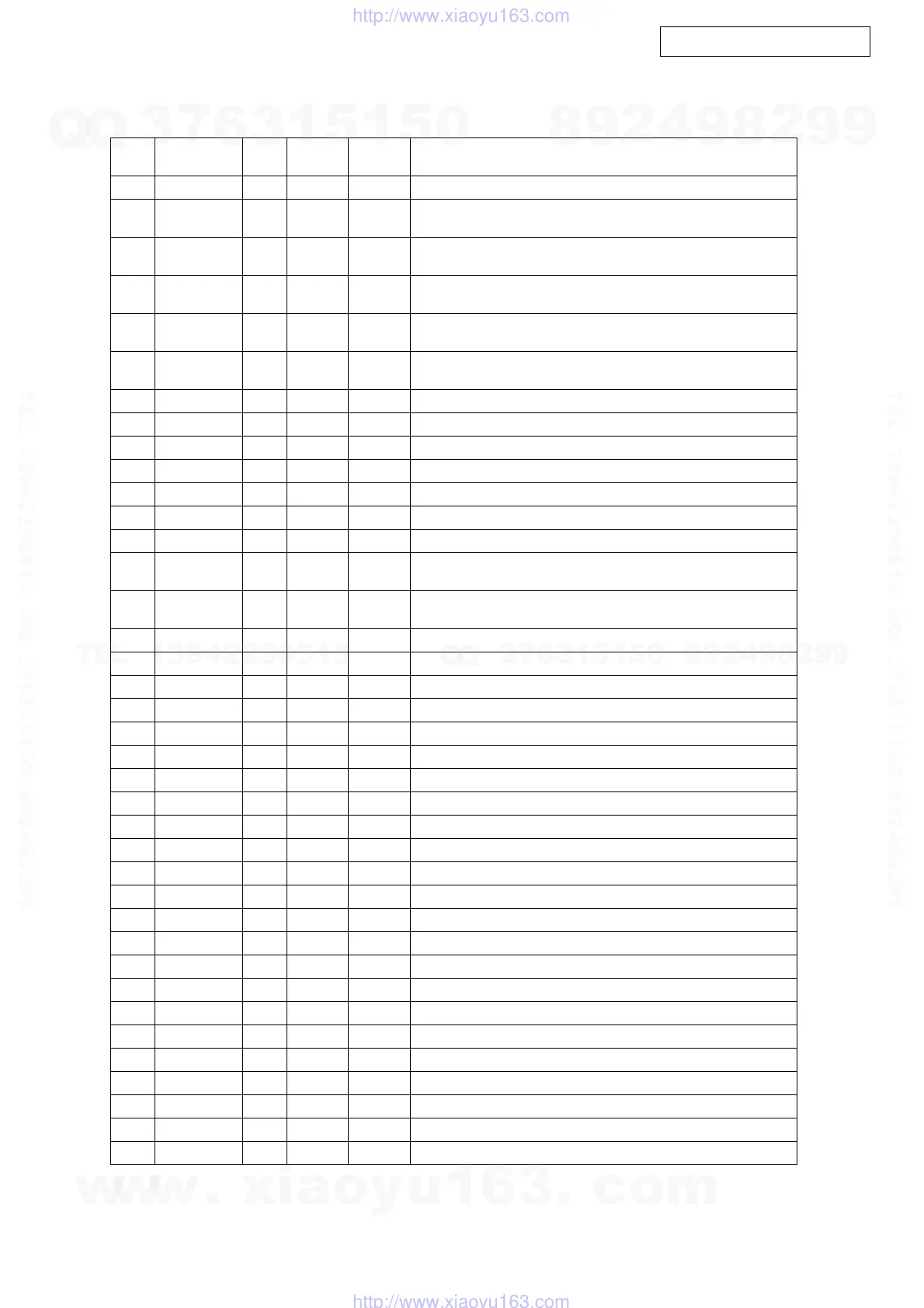

PIN DESCRIPTION

No. Name I/O Property

1

Input

voltage

Description

1 VDDL −− 2.5V Core power supply

2 SEL1FS I PD 3.3V

PCM output rate select 1

L: 2fs/4fs, H: fs

3 SEL4FS I PD 3.3V

PCM output rate select 2

L: 2fs, H: 4fs

4 SELEXT I PD 3.3V

fs/2fs/4fs output and external data output select

L: fs/2fs/4fs data, H: external data (EXI**)

5 DSGAIN I PD 3.3V

DSD signal gain setting

L: 100% modulation = 0dB, H: 50% modulation = 0dB

6 XMTPCM I PD 3.3V

PCM output mute control input

L: Mute ON, H: Mute OFF

7 VDDH −− 3.3V I/O power supply

8 TEST1 I PD 3.3V Test input 1 (must be open or tie LOW for normal operation)

9 TEST2 I PD 3.3V Test input 2 (must be open or tie LOW for normal operation)

10 TEST3 I PD 3.3V Test input 3 (must be open or tie LOW for normal operation)

11 TOUT1 O −−Test output 1

12 VSS −− −Ground

13 VDDL −− 2.5V Core power supply

14 DIRPCK I PD 3.3V

PCM output PBCK/PLRCK I/O select

L: Output (master mode), H: Input (slave mode)

15 FMTPCM I PD 3.3V

PCM output format select

L: MSB-first left-justified 32-bit, H: IIS 32-bit

16 VSS −− −Ground

17 MCKOUT O 12mA − System clock output (selected by SELEXT)

18 VDDH −− 3.3V I/O power supply

19 PBCK I/O S, 6mA 3.3V PCM output BCK bit clock

20 PLRCK I/O S, 6mA 3.3V PCM output LRCK word clock

21 POSLR O 2mA − PCM data output: surround left/right-channel

22 POCSW O 2mA − PCM data output: center/subwoofer channel

23 POFLR O 2mA − PCM data output: front left/right-channel

24 VSS −− −Ground

25 VDDL −− 2.5V Core power supply

26 TOUT2 O −−Test output 2

27 MCK I − 3.3V Master clock input: 512fs (22.5792MHz, fs = 44.1kHz)

28 VSS −− −Ground

29 EXIMCK I − 3.3V External system clock input

30 VDDH −− 3.3V I/O power supply

31 EXIBCK I S 3.3V External PCM data BCK bit clock input

32 EXILRCK I S 3.3V External PCM data LRCK word clock input

33 EXISLR I − 3.3V External PCM data input: surround left/right-channel

34 EXICSW I − 3.3V External PCM data input: center/subwoofer channel

35 EXIFLR I − 3.3V External PCM data input: front left/right-channel

36 VSS −− −Ground

37 VDDL −− 2.5V Core power supply

38 DSBCK I/O S, 6mA 3.3V DSD data input bit clock. Controlled by DIRDSCK

w

w

w

.

x

i

a

o

y

u

1

6

3

.

c

o

m

Q

Q

3

7

6

3

1

5

1

5

0

9

9

2

8

9

4

2

9

8

T

E

L

1

3

9

4

2

2

9

6

5

1

3

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299

http://www.xiaoyu163.com

http://www.xiaoyu163.com

Loading...

Loading...