RL78/G13 Handshake-based SPI Master Transmission/Reception

R01AN6883EJ0100 Rev.1.00 Page 11 of 38

June.15.23

2. Operation Confirmation Conditions

The operation of the sample code provided with this application note has been tested under the following

conditions.

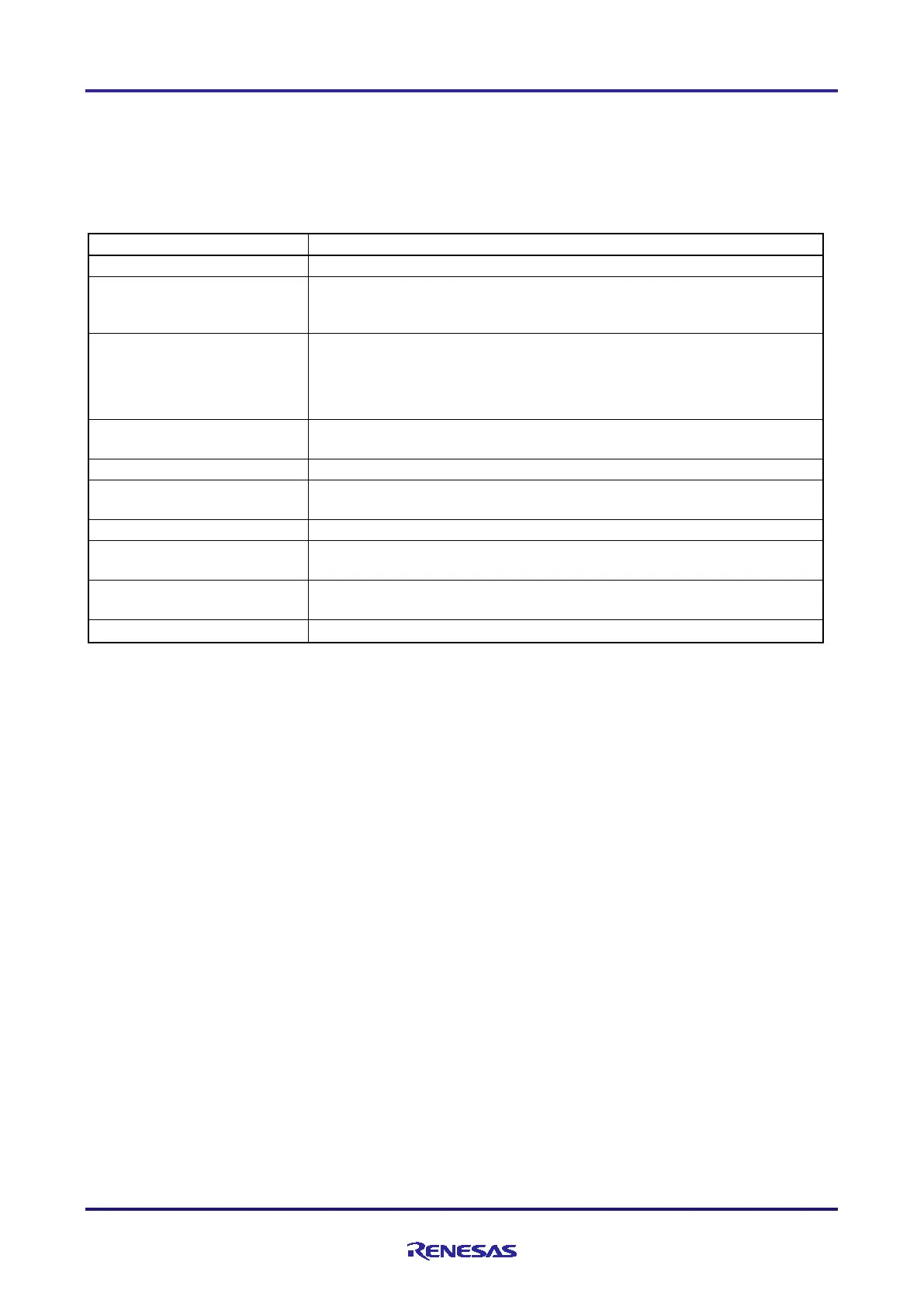

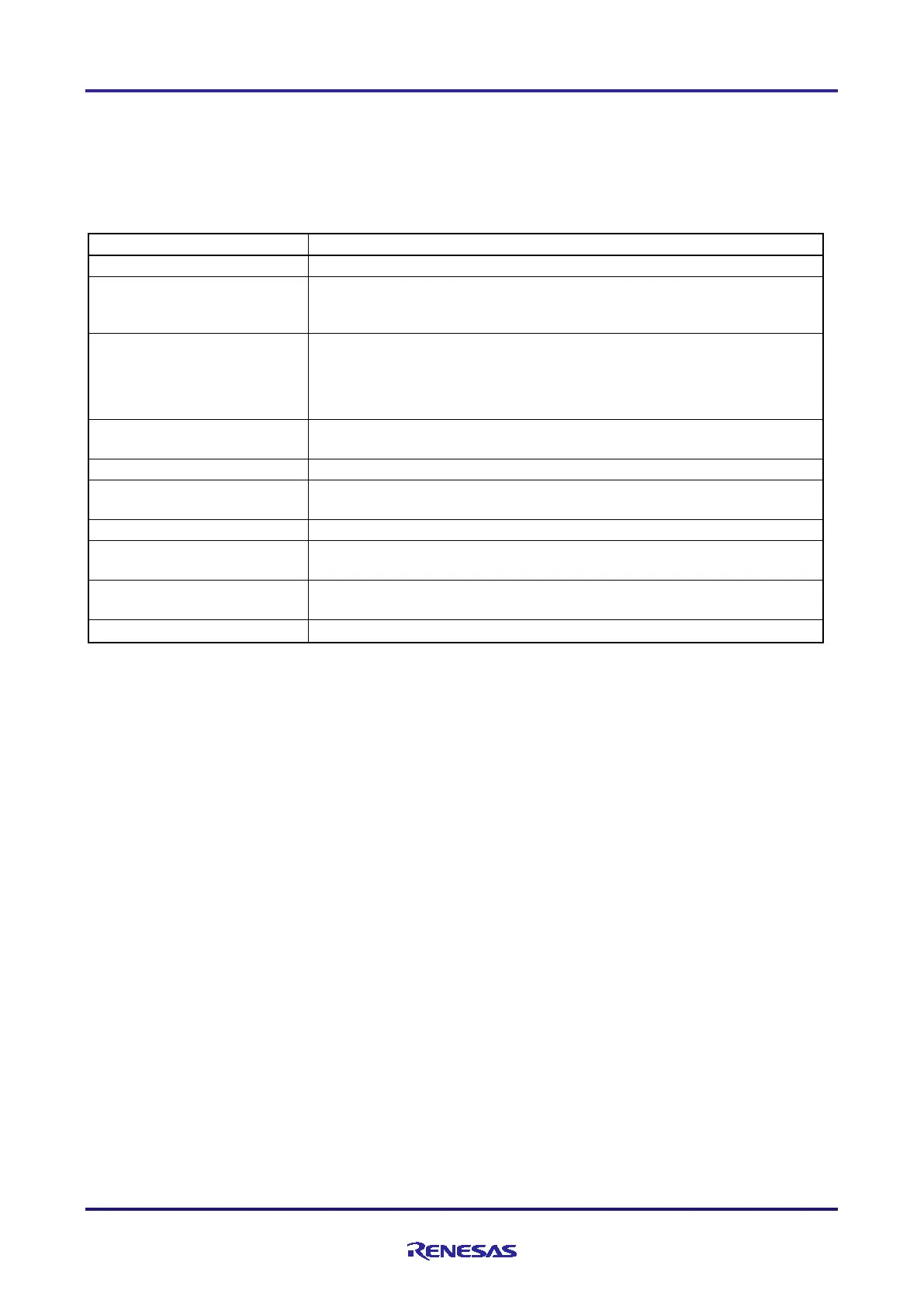

Figure 2-1 Operation Confirmation Conditions

High-speed on-chip oscillator clock (fIH): 32 MHz

CPU/peripheral hardware clock: 32 MHz

During VDD operation: 5.0 V

(

~

)

LVD detection voltage: Reset mode.

At rising edge TYP. 1.88V (1.84 V ~ 1.91 V)

At falling edge TYP. 1.84V (1.80 V

~

Integrated development

environment (CS+)

CS+ V8.09.00 from Renesas Electronics Corp.

CC-RL V1.12.00 from Renesas Electronics Corp

Integrated development

environment (e2studio)

e2 studio Version: 2023-01 (23.1.0) from Renesas Electronics Corp.

CC-RL V1.12.00 from Renesas Electronics Corp.

Integrated development

environment (IAR)

IAR Embedded Workbench for Renesas RL78 V4.21.2 from IAR

Systems Corp.

IAR C/C++ Compiler for Renesas RL78 V4.21.2.2420 from IAR Systems

Corp.

RL78/G13 (R5F100LE) Target Board

(

)

3. Related Application Notes

See also the following application notes, which are related to this application note:

RL78/G13 Handshake-based SPI Slave Transmission/Reception (R01AN6884E) APPLICATION NOTE

Loading...

Loading...