TB9100 Reciter Service Manual Network Circuitry 61

© Tait Electronics Limited January 2006

Parallel port pins that are not externally connected are set to outputs, so that

the internally connected paralleled inputs do not float.

5.3 Memory

Two types of memory are connected to the MPC main bus: flash EPROM

and synchronous DRAM (SDRAM). The flash EPROM is used mainly for

storing the boot loader, a Linux kernel image and a compressed flash file

system. The SDRAM is used as the main operating memory for storing

both code and data.

5.3.1 Flash Memory

Flash EPROM (U301) is a standard 32Mbit (2Mx16) chip. The PCB

footprint provides for an upgrade to a 64Mbit (4Mx16) chip for software

expansion. Both types of chip have an internally segmented block structure,

where each block can be individually erased or locked for protection. These

chips also incorporate a unique identifier code and an OTP protection area,

which can be used for product identification and software feature enabling.

See the data sheet (reference 3) for details of the operation of this chip.

Code does not normally execute out of the flash EPROM, except during

the boot load process: it is quite slow due to the need for performing two

16-bit memory fetches per 32-bit instruction for the MPC. The slow access

time (70ns) of the flash also further slows execution speed, as five wait states

have to be added to each memory cycle. The addition of wait states and

other signal timing requirements are implemented by the GPCM (see

“General-Purpose Chip Select Machine” on page 50).

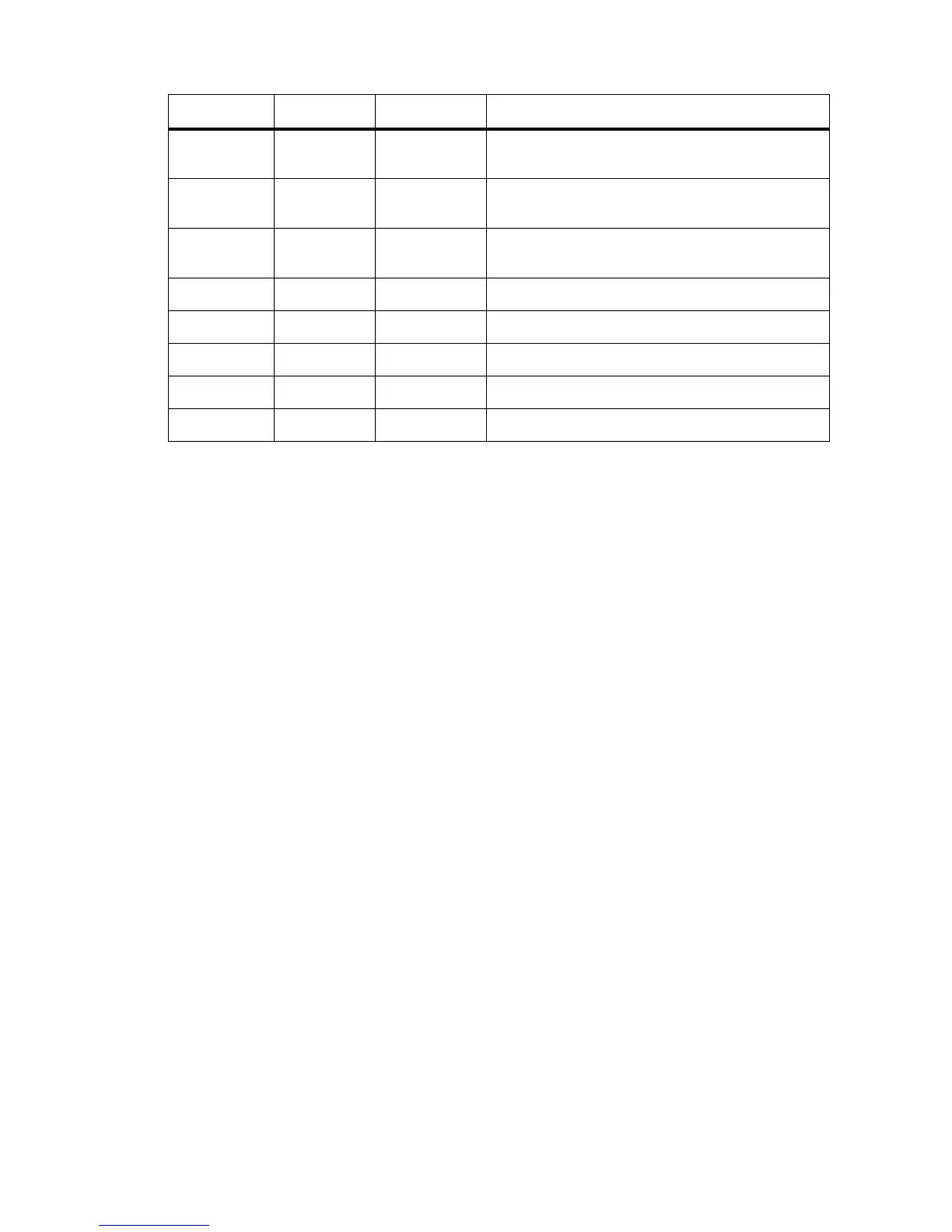

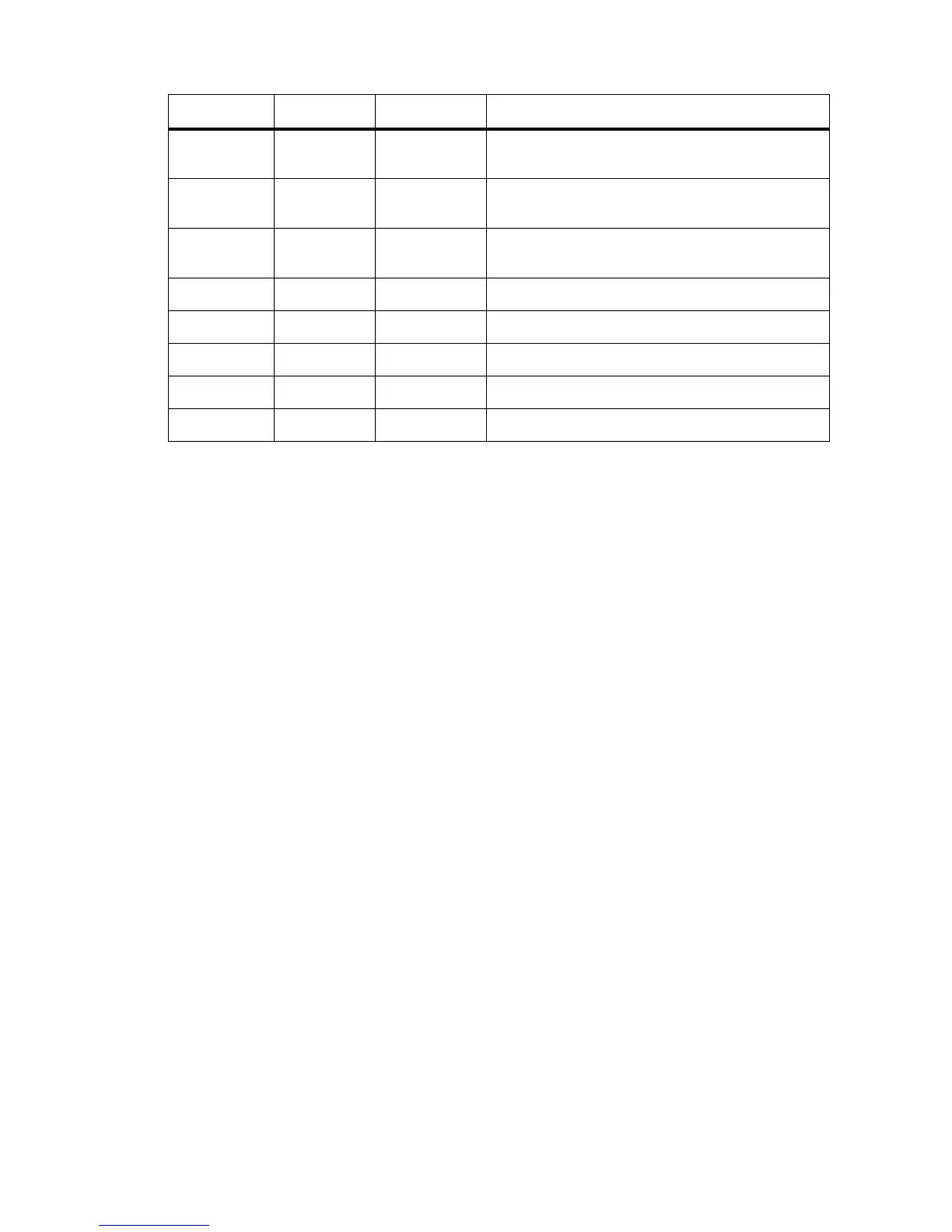

IPA3 I/P General purpose

digital input 3

“General-purpose Digital Inputs” on page 72

IPA4 I/P General purpose

digital input 4

“Antenna Relay Control” on page 73

IPA5 I/P General purpose

digital input 5

IPA6 I/P Rx gate input

IPA7 I/P Co-ax relay input

OP1 O/P none

OP2 O/P none

OP3 O/P none

Table 5.9 Parallel I/O Ports (Continued)

Pin Name Direction Function Reference

Loading...

Loading...