19

AVR-1707/1507/687/587/487

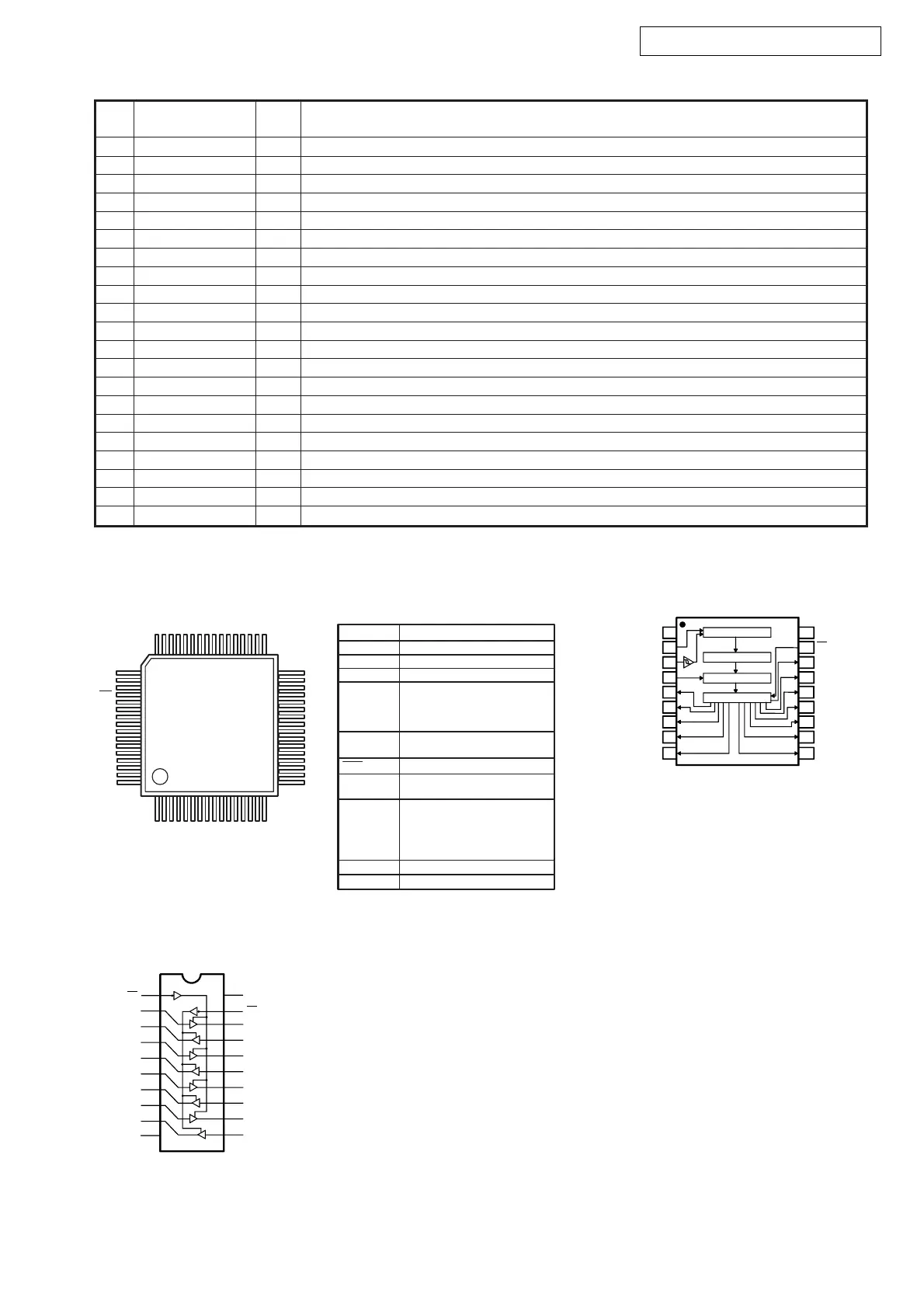

LC75721E (IC301) BU2090F (IC302,1005,1008)

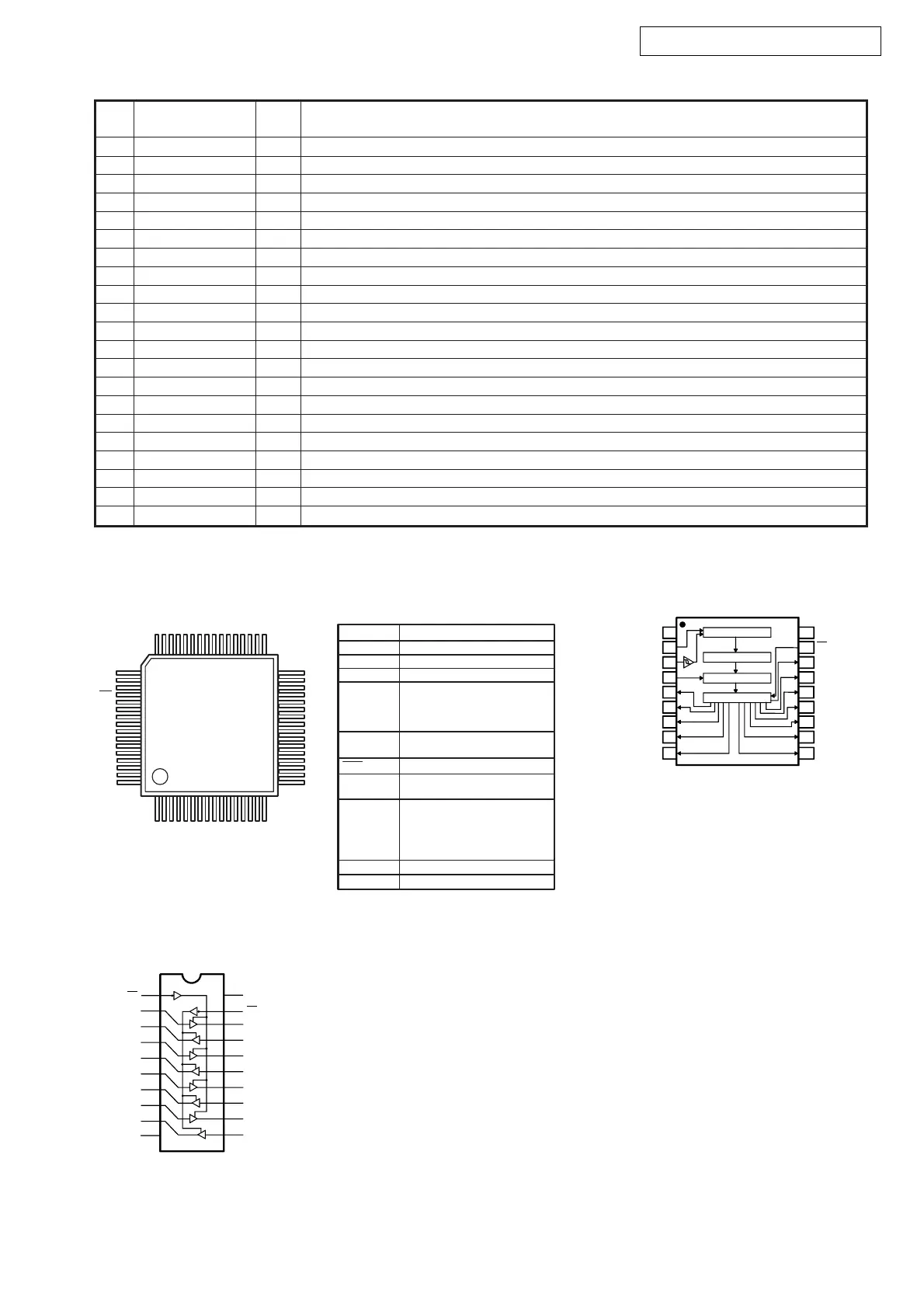

MM74LCX244 (IC809-811)

Function

Pin

No.

Pin Name I/O

* For latch-up countermeasure, perform each power supply ON/OFF in the same timing.

28 XOUT O X’tal osc. connecting output terminal

29 XIN I X’tal osc. connection, external clock input terminal (24.576MHz or 12.288MHz)

30 DVDD — Digital power

31 DGND — Digital GND

32 EMPHA/UO I/O Emphasis information/U-data output/Chip address setting terminal

33 AUDIO/VO I/O Non-PCM detect/V-flag output/ Chip address setting terminal

34 CKST I/O Clock switch transition period output/Demodulation master or slave function switching terminal

35 INT I/O Interrupt output for µcom (Interrupt factor selectable)/Modulation or general I/O switching terminal

36 RERR O PLL lock error, data error flag output

37 DO O µcom I/F, read out data output terminal (3-state)

38 DI I µcom I/F, write data input terminal

39 CE I µcom I/F, chip enable input terminal

40 CL I µ com I/F, clock input terminal

41 XMODE I System reset input terminal

42 DGND — Digital GND

43 DVDD — Digital power

44 TMCK/PIO0 I/O 256fs system clock input for modulation/General I/O in/output terminal

45 TBCK/PIO1 I/O 64fs bit clock input for modulation/General I/O in/output terminal

46 TLRCK/PIO2 I/O fs clock input for modulation/General I/O in/output terminal

47 TDATA/PIO3 I/O Serial audio data input for modulation/General I/O in/output terminal

48 TXO/PIOEN O/I Modulation data output/ General I/O enable input terminal

64

49

48 33

32

17

161

AM 1

AM 2

AM 3

AM 4

AM 5

AM 6

AM 7

AM 8

AM 9

AM 10

AM 11

AM 12

AM 13

AM 14

AM 15

AM 16

AM 17

AM 18

AM 19

AM 20

AM 21

AM 22

AM 23

AM 24

AM 25

AM 26

AM 27

AM 28

AM 29

AM 30

AM 31

AM 32

G7

G8

G9

G10

G11

AA8/G12

AA7/G13

AA6/G14

AA5/G15

AA4/G16

AA3

AA2

AA1

AM35

AM34

AM33

DI

CL

CE

RES

V

DD

OSCI

OSCO

Vss

TEST

V

FL

G1

G2

G3

G4

G5

G6

Symbol

V

DD

Vss

Power terminal +5V

Power terminal GND

V

FL

Power terminal FL drive

DI

CL

CE

Serial data transfer terminal

DI: Data

CL: Clock

CE: Chip enable

OSCI

OSCO

External CR connecting terminal

RES

System reset terminal

AM1~AM35

AA1~AA3

Anode output terminal

AA4/G16

AA5/G15

AA6/G14

AA7/G13

AA8/G12

Anode/Grid output terminal

G1~G11 Grid output terminal

TEST LSI test terminal

Function

LC75721E Terminal Function

1

2

3

4

5

6

7

8

20

19

18

16

15

14

13

I3

VCC

OE2

O2

I5

O0

I4

O1

I6

OE

I0

O4

I1

O5

I2

O6

912

O7 O3

10 11

GND

I7

TOP VIEW

17

1

2

3

4

5

6

7

8

18

17

16

15

14

13

12

11Q3

VDD

OE

Q7

Q8

Q11

Q10

Q9

Q6

VSS

DATA

CLOCK

LCK

Q0

Q1

Q2

9

10

Q4

Q5

CONTROL CIRCUIT

12-bit SHIFT REGISTER

12- bi t STRAGE REGI STER

OUTPUT BUFFER ( OPEN DRA I N)

Loading...

Loading...