Intel® Server Board S1200SP Family Technical Product Specification

123

S3 Resume PEIM (S3 started)

S3 Resume PEIM (S3 boot script)

S3 Resume PEIM (S3 Video Repost)

S3 Resume PEIM (S3 OS wake)

PEIM which detected forced Recovery condition

PEIM which detected User Recovery condition

Recovery PEIM (Recovery started)

Recovery PEIM (Capsule found)

Recovery PEIM (Capsule loaded)

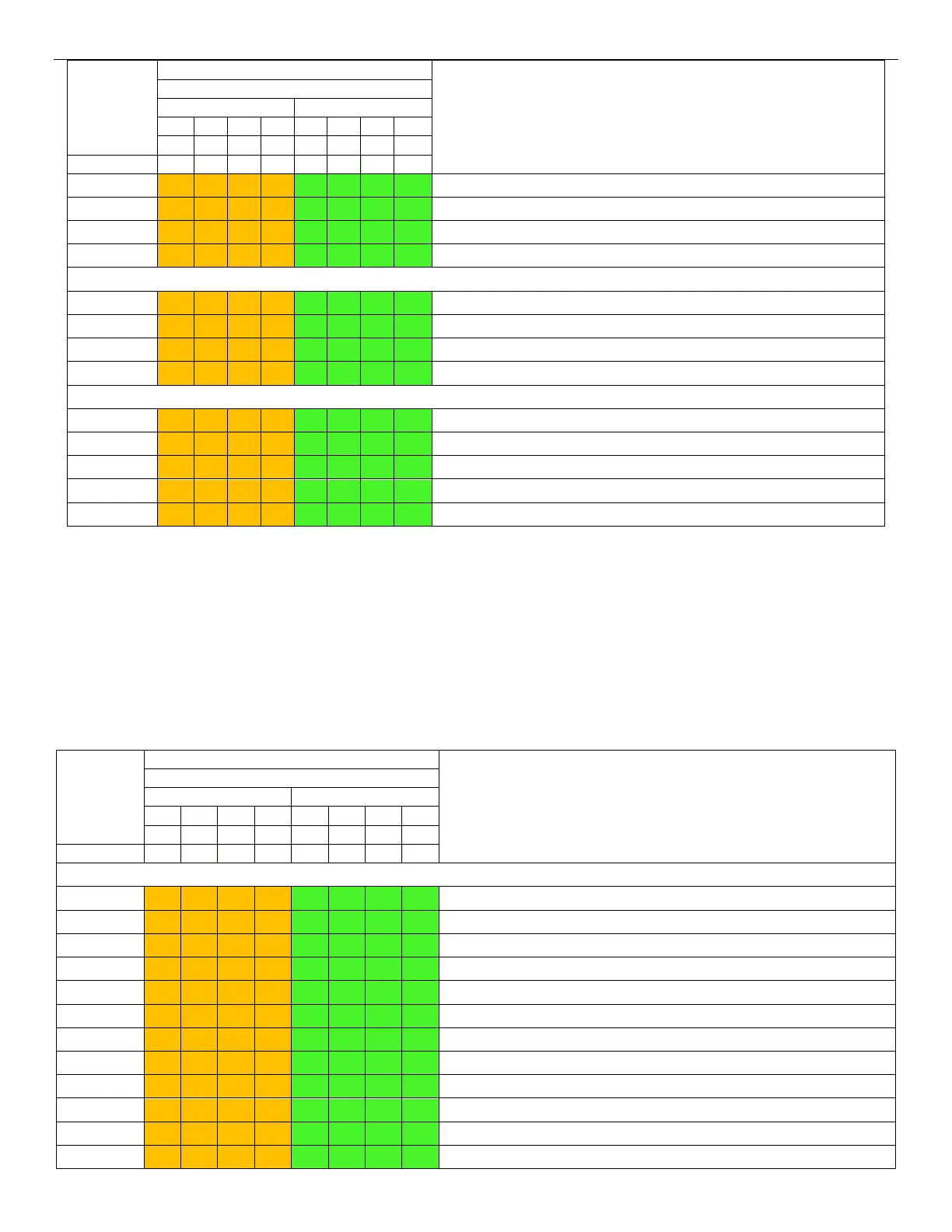

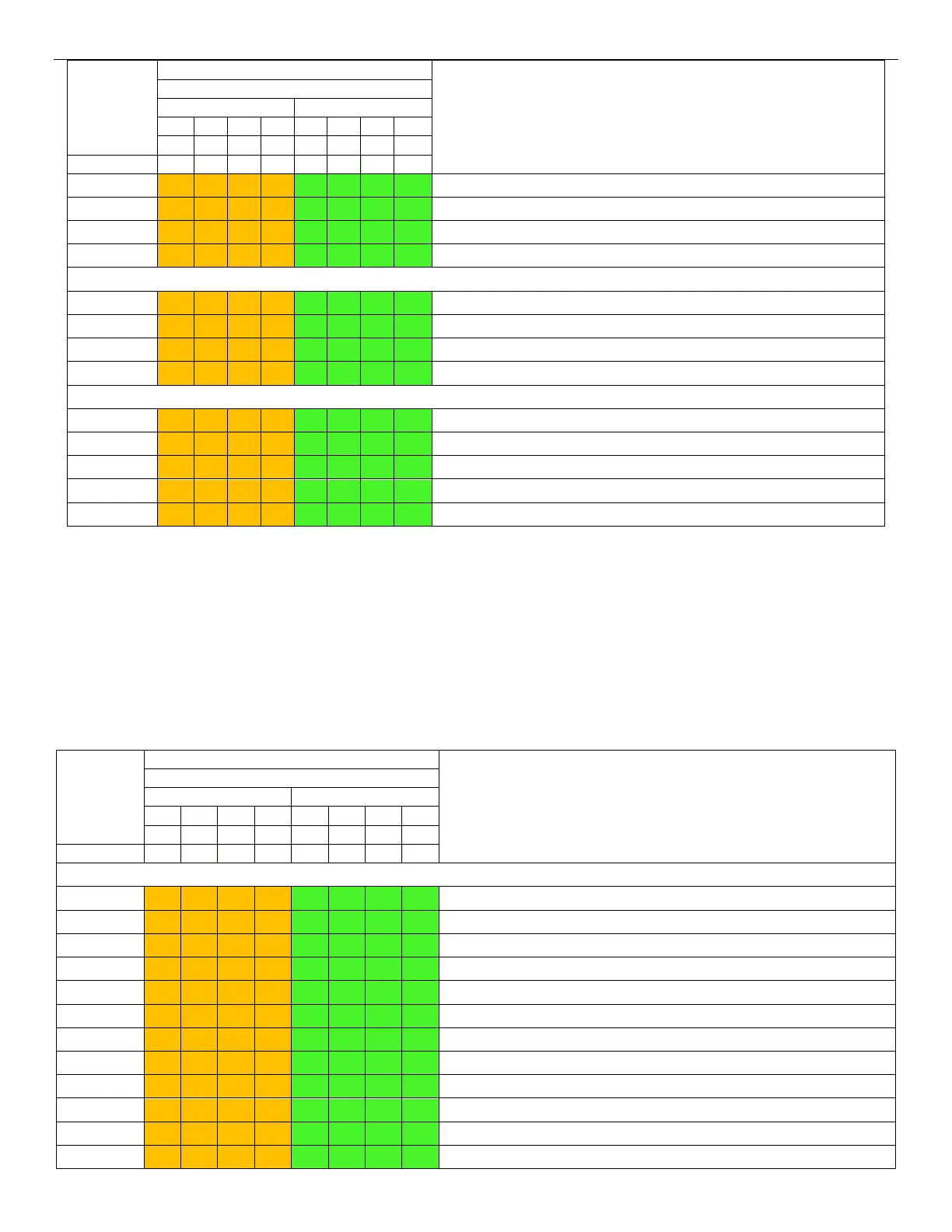

POST Memory Initialization MRC Diagnostic Codes

There are two types of POST Diagnostic Codes displayed by the MRC during memory initialization; Progress

Codes and Fatal Error Codes.

The MRC Progress Codes are displays to the Diagnostic LEDs that show the execution point in the MRC

operational path at each step.

Table 63. MRC Progress Codes

Gather remaining SPD data

Program registers on the memory controller level

Evaluate RAS modes and save rank information

Program registers on the channel level

Perform the JEDEC defined initialization sequence

Hardware memory test and init

Execute software memory init

Program memory map and interleaving

Loading...

Loading...