5. SEQUENCE INSTRUCTIONS

5 − 5

MELSEC-A

5.2 Connection Instructions

5.2.1 Ladder block series connection,

parallel connection (ANB, ORB)

Available Device

Bit device Word (16-bit) device Constant Pointer Level

Carry

flag

Error

flag

X Y M L S B F T C D W R A0 A1 Z V K H P I N

Digit specification

Index

M9012 (M9010, M9011)

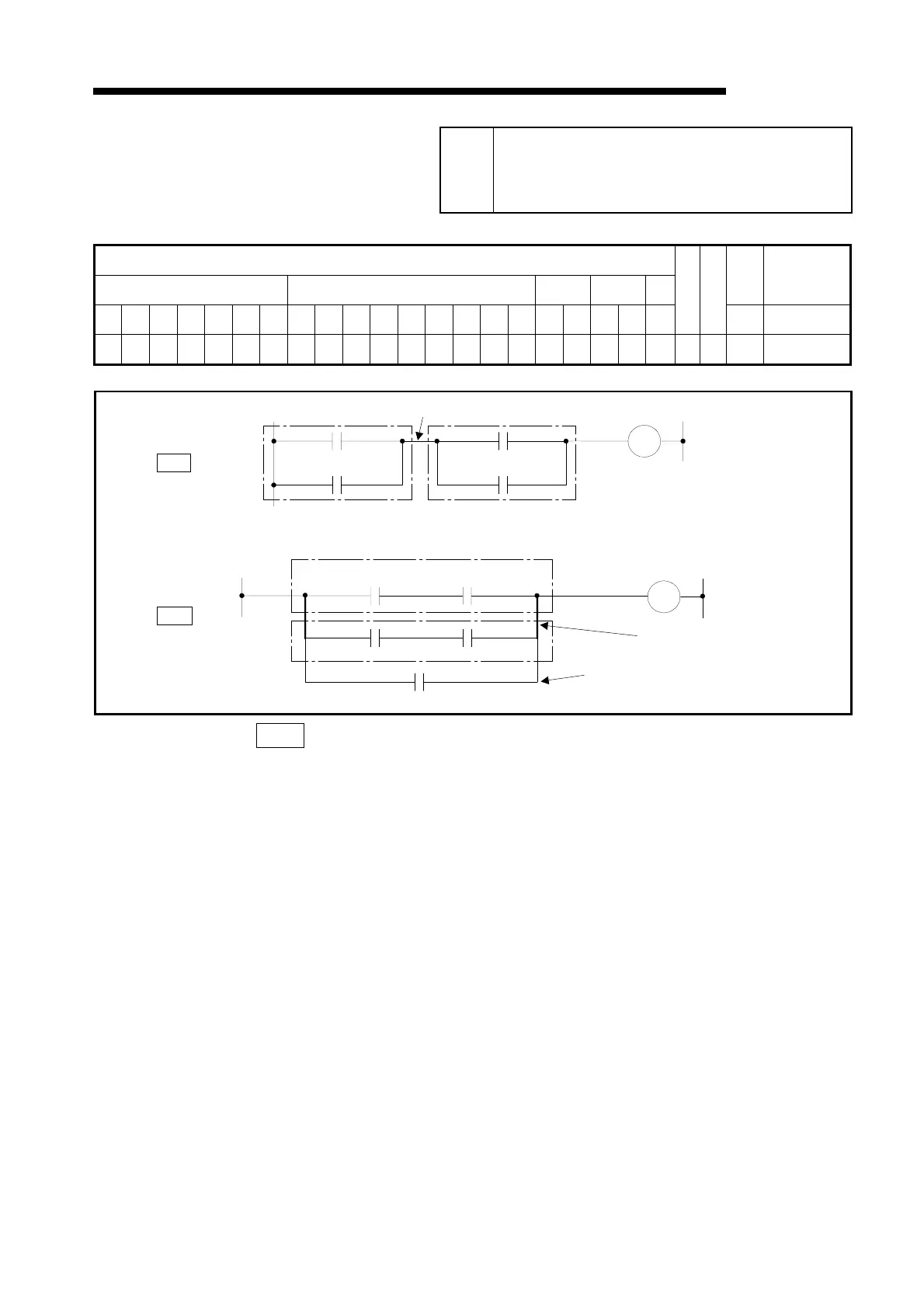

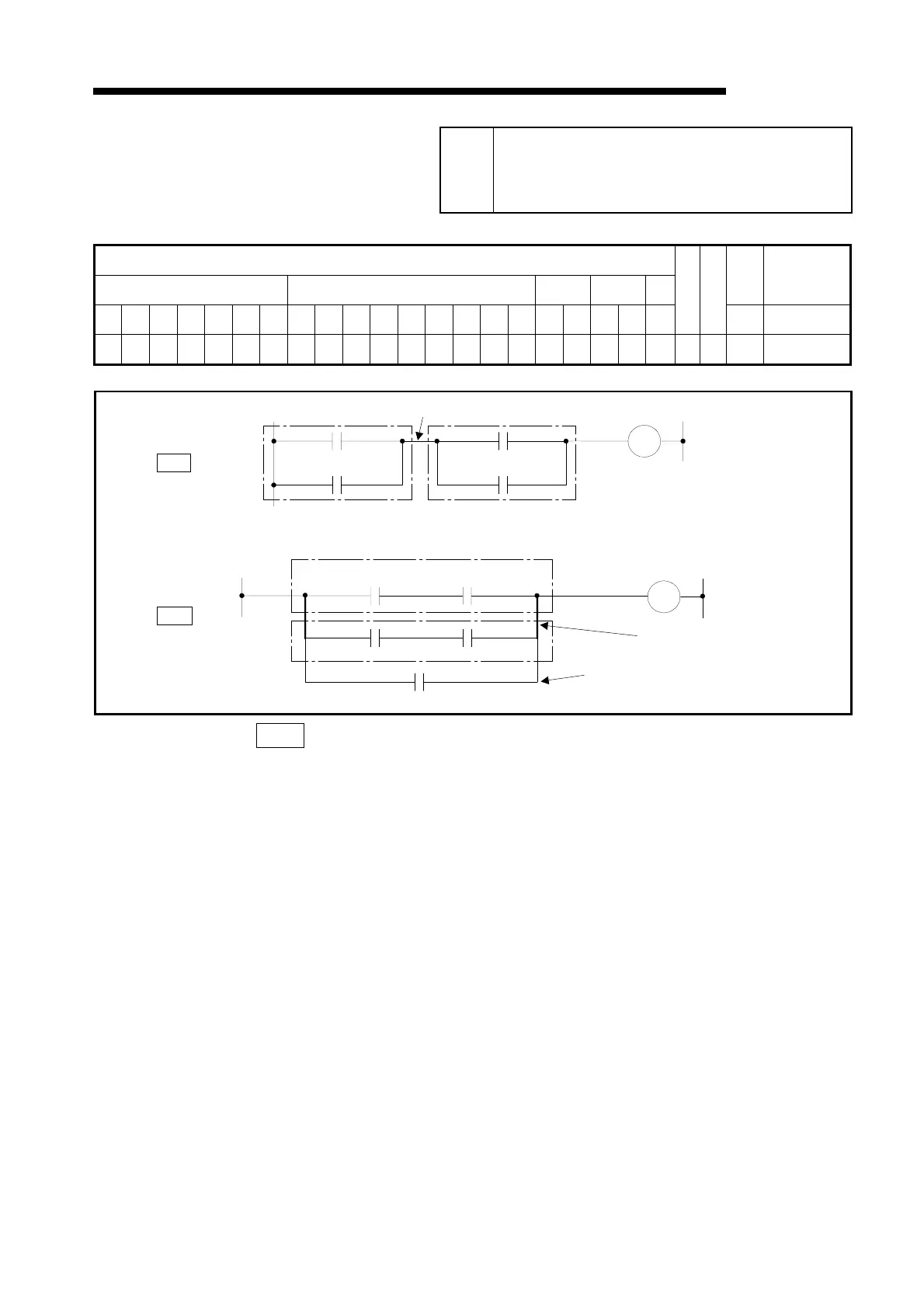

Functions ANB

(1) This instruction performs the AND operation of block A and Block B, and uses it

as an operation result.

(2) The symbol of ANB is not a contact symbol but a connection symbol.

(3) ANB can be written consecutively up to the number of instructions mentioned

below.

For AnA, A2AS, AnU, QCPU-A (A Mode) and A2USH board

: 15 instructions (16 blocks)

For CPUs other than AnA, A2AS, AnU, QCPU-A (A Mode) and A2USH board

: 7 instructions (8 blocks)

If more ANBs are written consecutively, the PC cannot perform proper

operation.

Applicable

CPU

All CPUs

ANB

Block A

Block B

ORB

Block A

Block B

For the parallel connection of one contact,

use OR or ORI.

ANB

ORB

Loading...

Loading...