6-14 | ni.com

Chapter 6 Digital I/O

• Counter n Internal Output

• Frequency Output

• DI Change Detection output

Several other internal signals can be routed to DO Sample Clock through internal routes. Refer

to Device Routing in MAX in the NI-DAQmx Help or the LabVIEW Help for more information.

Using an External Source

Use one of the following external signals as the source of DO Sample Clock:

• PFI <0..15>

•RTSI <0..7>

• PXI_STAR

• PXIe_DSTAR<A,B>

• Analog Comparison Event (an analog trigger)

Routing DO Sample Clock to an Output Terminal

You can route DO Sample Clock (as an active low signal) out to any PFI <0..15>, RTSI <0..7>,

or PXIe_DSTARC terminal.

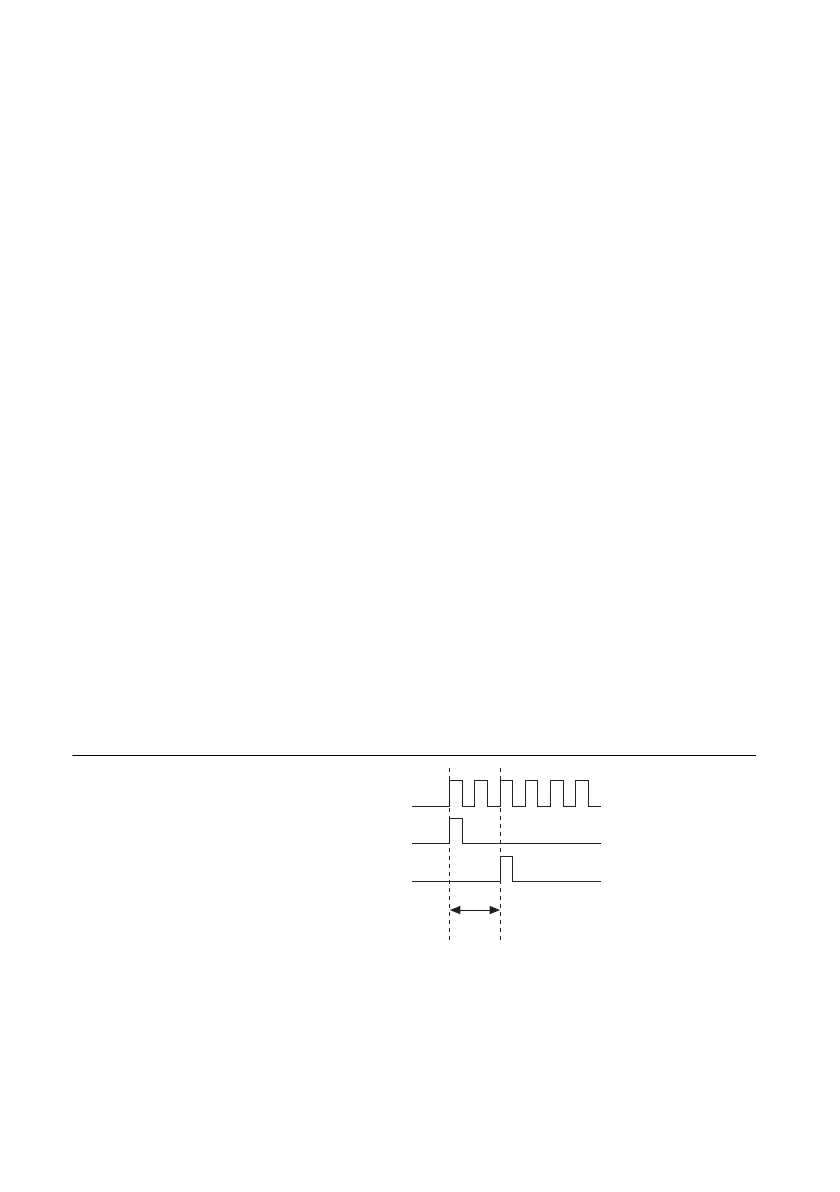

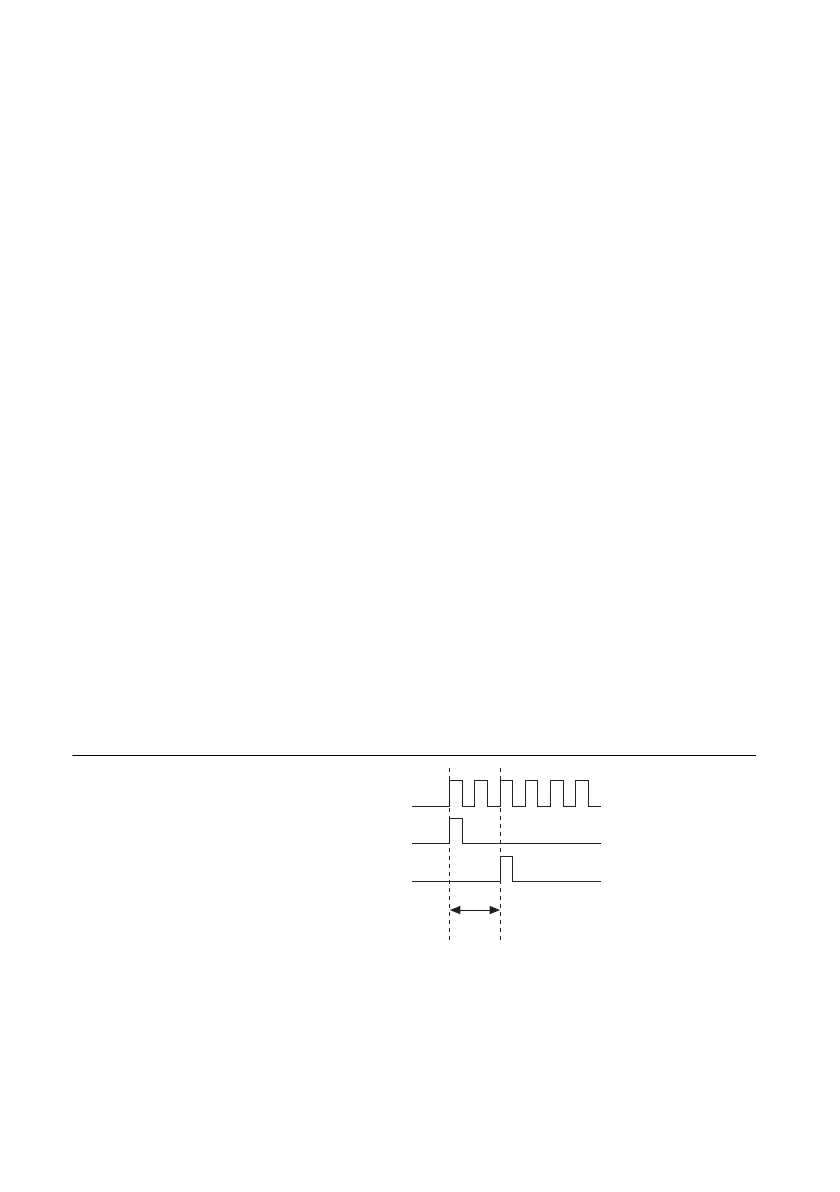

Other Timing Requirements

The DO timing engine on your device internally generates DO Sample Clock unless you select

some external source. DO Start Trigger starts the timing engine and either the software or

hardware can stop it once a finite generation completes. When using the DO timing engine, you

can also specify a configurable delay from DO Start Trigger to the first DO Sample Clock pulse.

By default, this delay is two ticks of DO Sample Clock Timebase. Figure 6-7 shows the

relationship of DO Sample Clock to DO Start Trigger.

Figure 6-7. DO Sample Clock and DO Start Trigger

DO Sample Clock Timebase

DO Start Trigger

DO Sample Clock

Delay

From

Start

Trigger

Loading...

Loading...