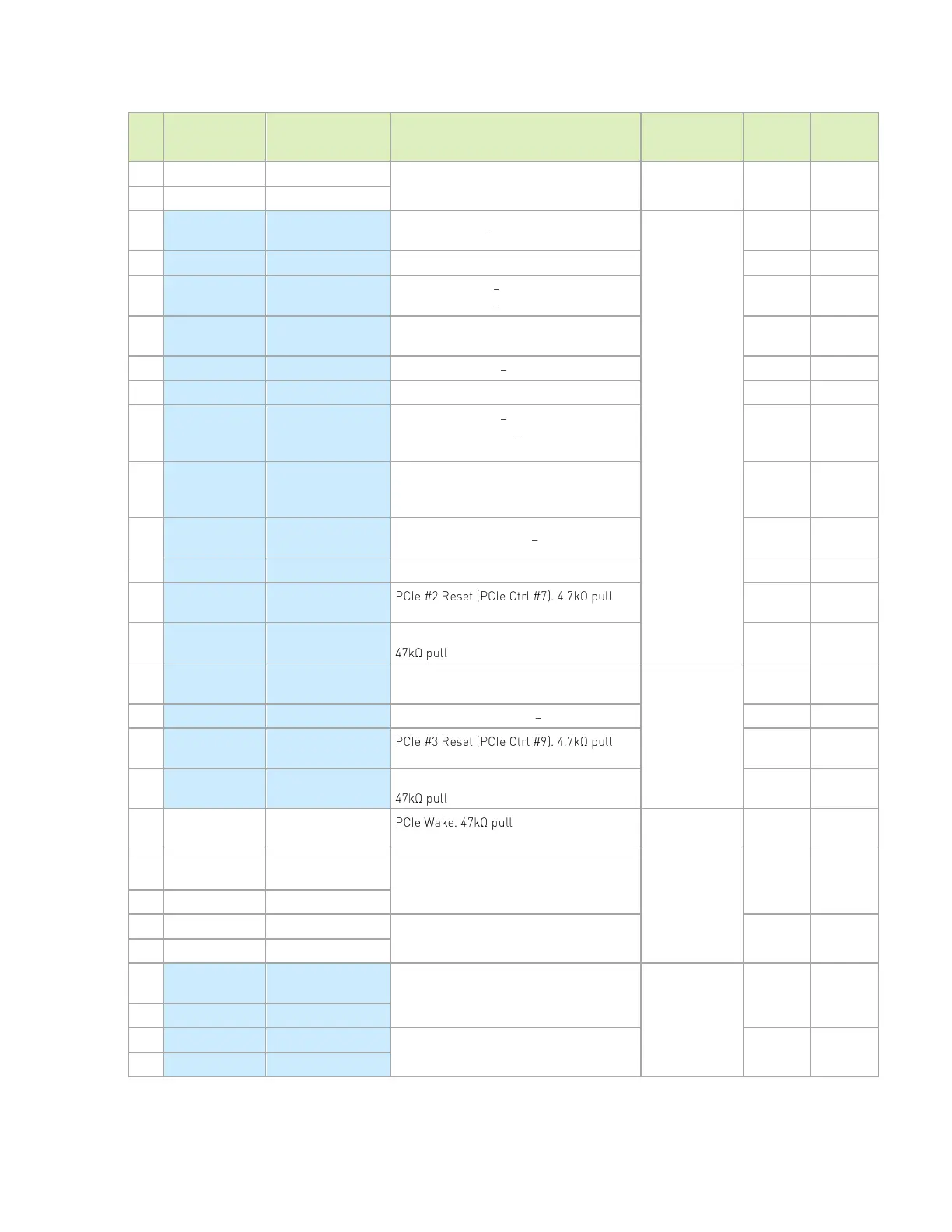

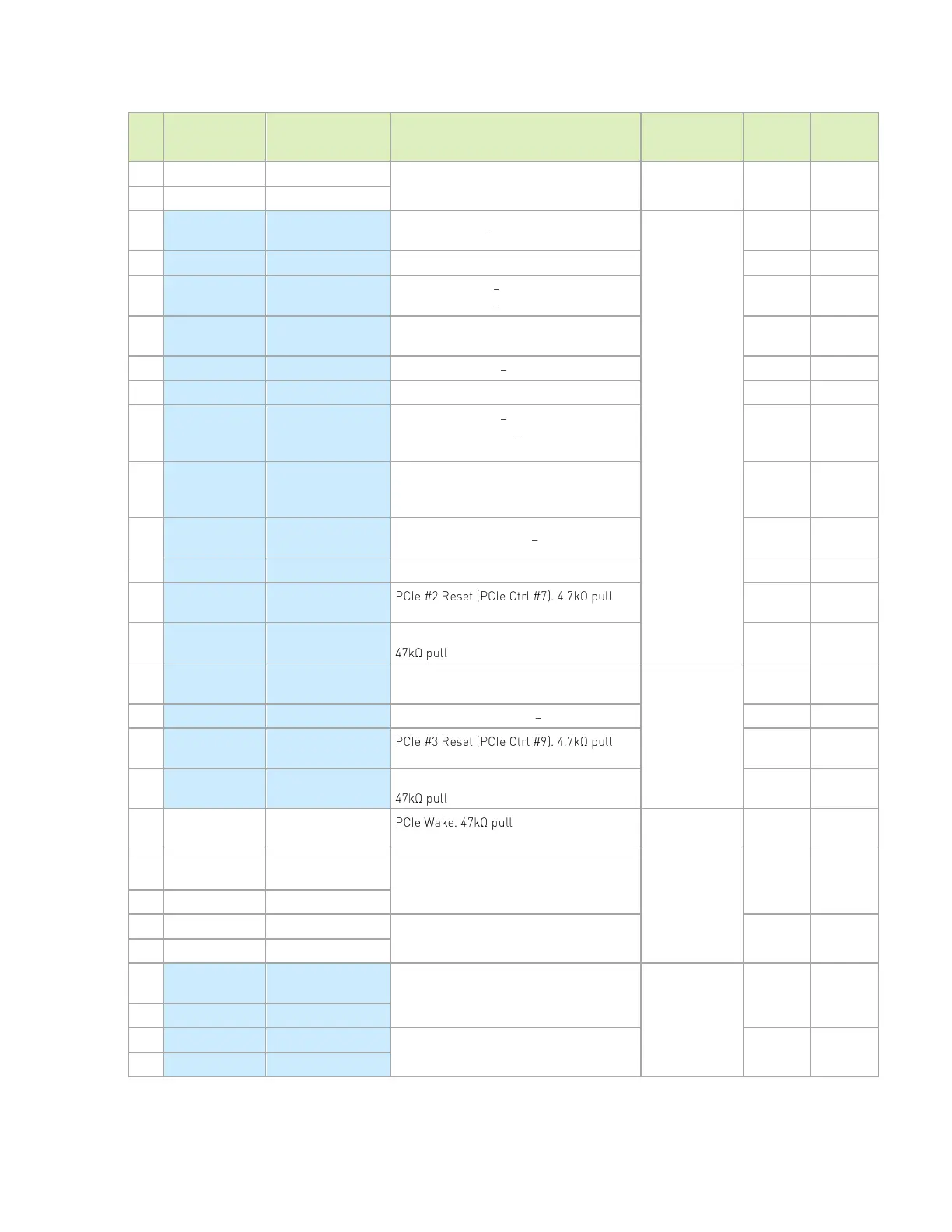

USB and PCIe

PRELIMINARY INFORMATION

Jetson Orin NX Series and Jetson Orin Nano Series DG-10931-001_v1.1 | 28

Orin SoC Pin Name

(See Note 4)

PCIe #1 Reference Clock (PCIe Ctrl #1)

PCIe 2 Receive 0 (PCIe Ctrl #7 Lane 0)

PCIe x2 (Ctrl #7)

or 2 x PCIe x1

(Ctrl #7 and Ctrl

#9)

PCIe 2 Receive 0+ (PCIe Ctrl #7 Lane 0)

PCIe #2 Receive 1 (PCIe Ctrl #7 Lane 1) or

PCIe #3 Receive 0 (PCIe Ctrl #9 Lane 0)

PCIe #2 Receive 1+ (PCIe Ctrl #7 Lane 1) or

PCIe #3 Receive 0+ (PCIe Ctrl #9 Lane 0)

PCIe #2 Transmit 0 (PCIe Ctrl #7 Lane 0)

PCIe #2 Transmit 0+ (PCIe Ctrl #7 Lane 0)

PCIe #2 Transmit 1 (PCIe Ctrl #7 Lane 1)

or PCIe #3 Transmit 0 (PCIe Ctrl #9 Lane

0)

PCIe #2 Transmit 1+ (PCIe Ctrl #7 Lane 1)

or PCIe #3 Transmit 0+ (PCIe Ctrl #9 Lane

0)

PCIe #2 Reference Clock (PCIe Ctrl #7)

PCIe #2 Reference Clock+ (PCIe Ctrl #7)

-up

to 3.3V on the module.

PCIE #2 Clock Request (PCIe Ctrl #7).

-up to 3.3V on the module.

PCIe #3 Reference Clock+ (PCIe Ctrl #9)

PCIe #3 Reference Clock (PCIe Ctrl #9)

-up

to 3.3V on the module.

PCIE #3 Clock Request (PCIe Ctrl #9).

-up to 3.3V on the module.

-up to 3.3V on the

module.

Shared between

PCIe interfaces.

USB 3.2 Receive (Port #0)

USB 3.2

connector,

device or hub

USB 3.2 Transmit (Port #0)

USB 3.2 Receive (Port #1)

USB 3.2

connector,

device or hub

USB 3.2 Transmit (Port #1)

Loading...

Loading...