USB and PCIe

PRELIMINARY INFORMATION

Jetson Orin NX Series and Jetson Orin Nano Series DG-10931-001_v1.1 | 36

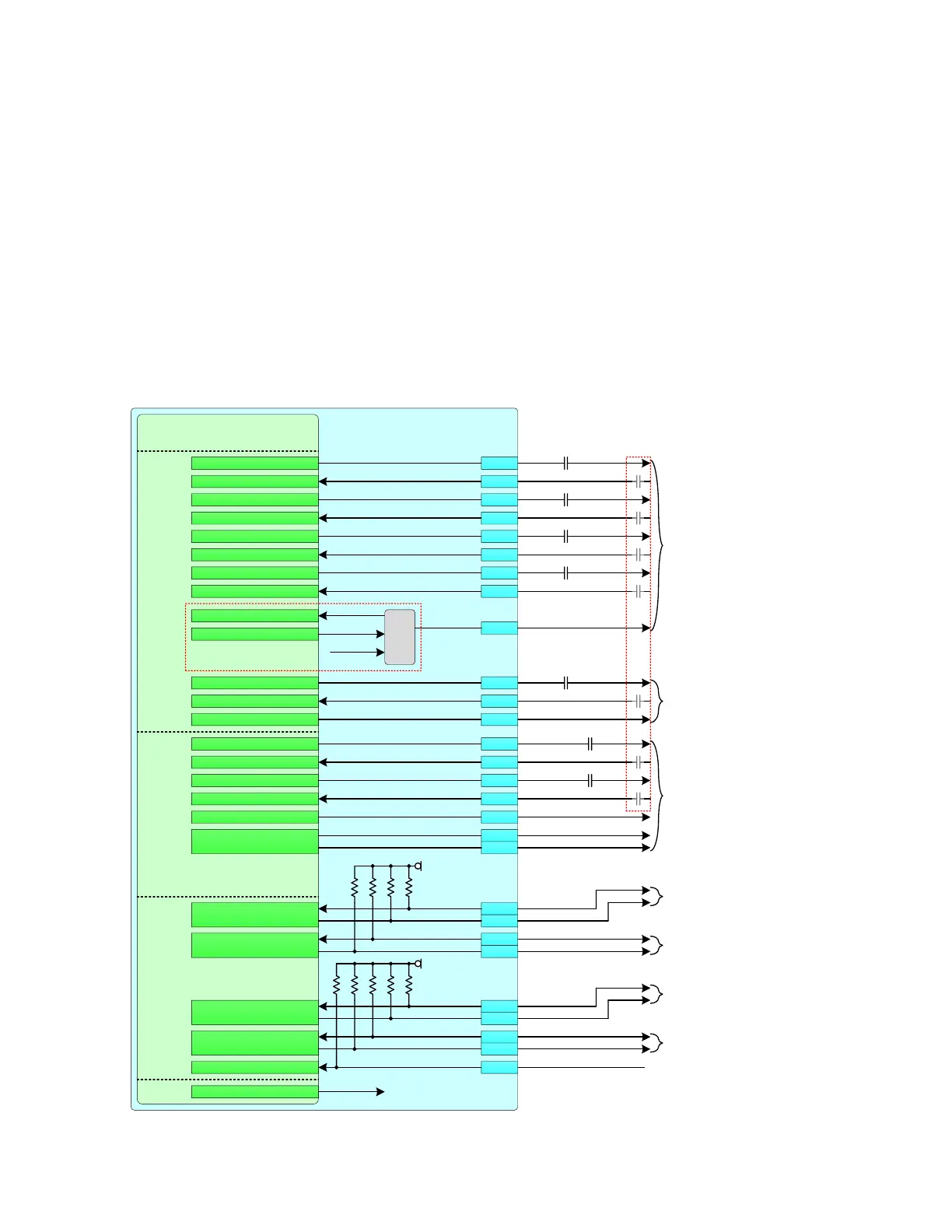

7.2 PCIe

Orin module brings four PCIe interfaces to the module pins for up to seven total lanes (1 x4 + 1

x1 + 1x2) for use on the carrier board. The PCIe x4 interface (PCIE0) operates up to Gen4 speed

and supports both Root Port and Endpoint operation. The PCIe x1 interface (PCIE1) operates

up to Gen4 speed and support only Root Port operation. The PCIe x2 interface (PCIE2) can also

be broken into two x1 interfaces (PCIE2 x1 and PCIE3 x1). PCIE2 and PCIE3 operate up to Gen4

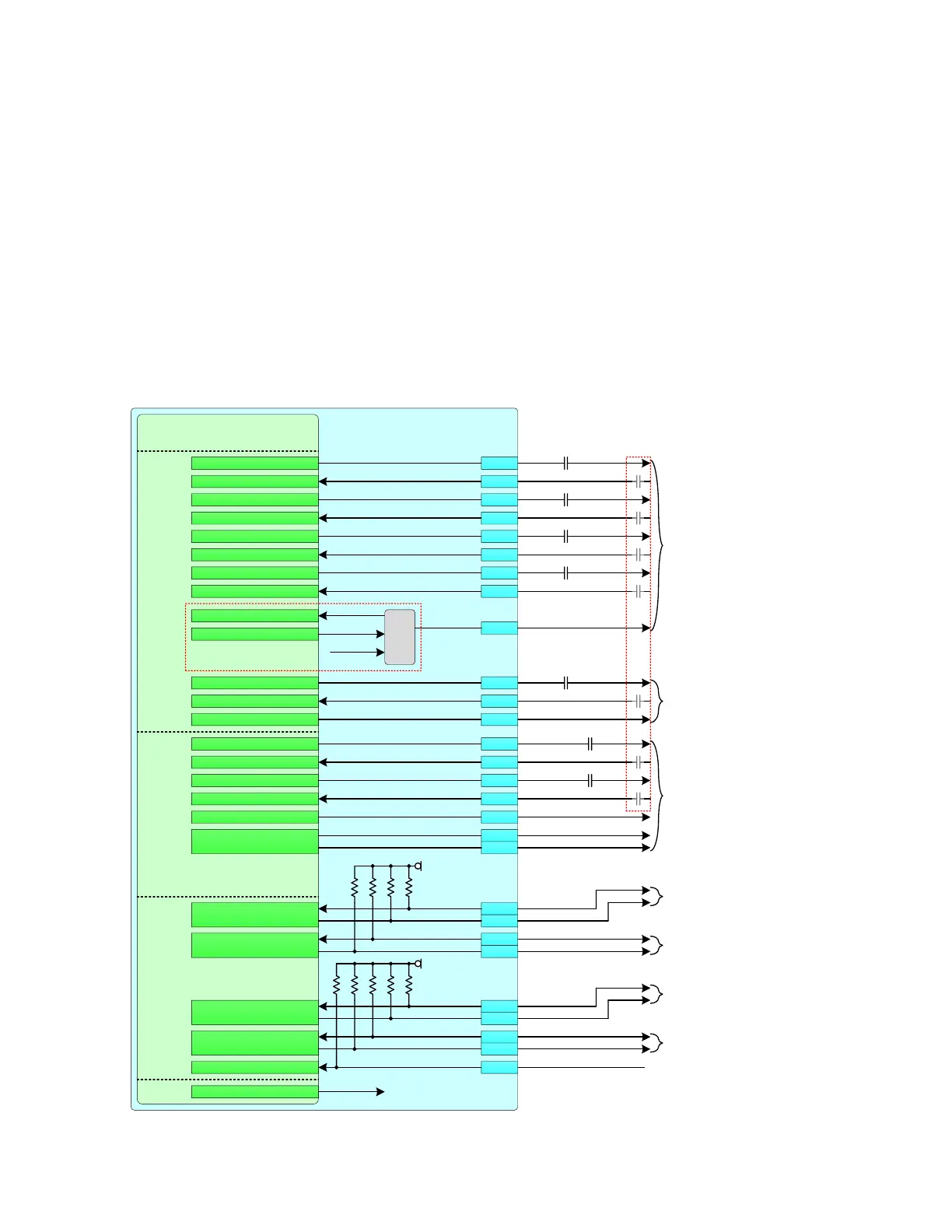

speed and support only Root Port operation. Figure 7-5 shows all possible interfaces as Root

Ports. Figure 7-6 shows the x4 interfaces as an Endpoint. Lane reversal and polarity inversion

(P/N swapping) is supported per controller.

Figure 7-5. PCIe Root Port Connections Example

Loading...

Loading...