Add Normalized

(AER)

(AE) (ADR) (AD)

General Description

Format

(RR

Short)

(RX Short)

(RR

Long)

(RX Long)

Condition Code

Interrupt

Action

Floating-Point Instructions

• The operand specified by

the

second address

(R

2

or

XdBdD

2

)

is added

to

the

operand in

the

floating-point

register

specified by

the

first address

(R

1

).

The normalized sum is loaded into

the

register

specified by

the

first

address. The sign

and

magnitude

of

the

sum determine

the

condition code.

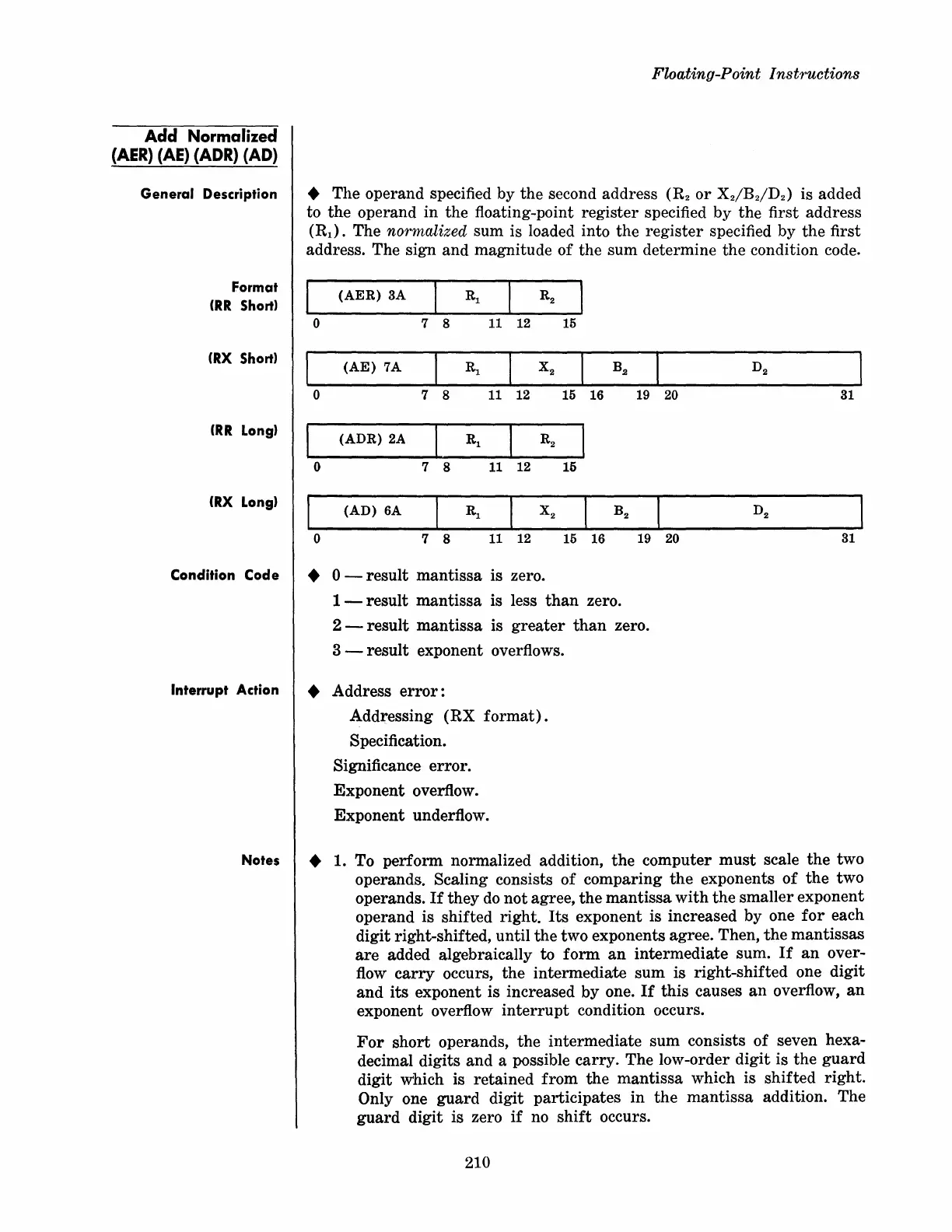

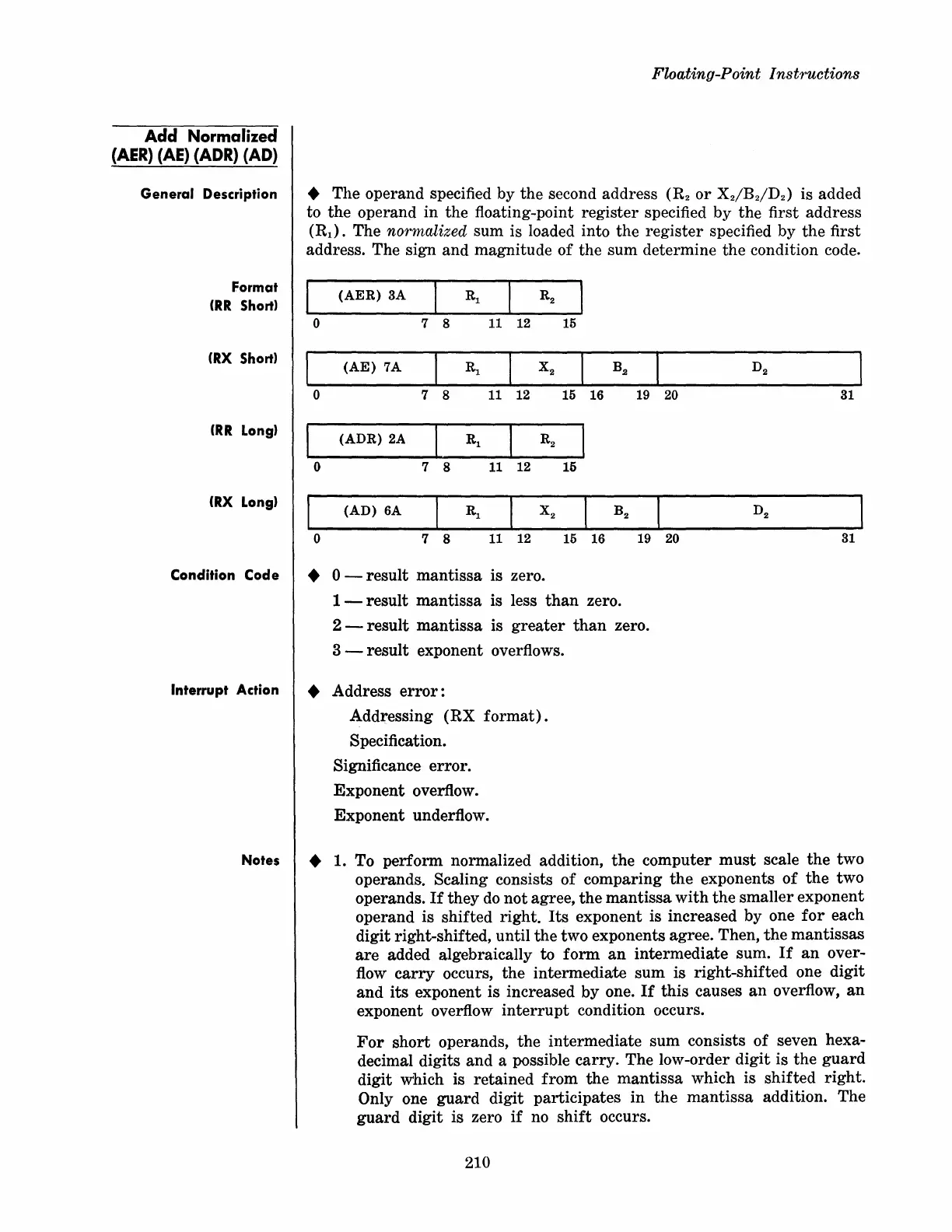

(AER)

3A

R1

R2

0 7

8

11

12

15

(AE)

7A

R1

X

2

B2

0

7 8 11

12

15

16

19

20

31

(ADR)

2A

R1

R2

0 7

8 11

12

15

(AD)

6A

~

X

2

B2

0

7 8

11

12

15

16

19

20

31

•

o -

result

mantissa

is zero.

1 - result

mantissa

is less

than

zero.

2 - result

mantissa

is

greater

than

zero.

S - result exponent overflows.

•

Address

error:

Addressing (RX

format).

Specification.

Significance

error.

Exponent

overflow.

Exponent underflow.

Notes • 1. To

perform

normalized addition,

the

computer

must

scale

the

two

operands. Scaling consists

of

comparing

the

exponents

of

the

two

operands.

If

they

do

not

agree,

the

mantissa

with

the

smaller exponent

operand is shifted right.

Its

exponent is increased by one

for

each

digit right-shifted, until

the

two exponents agree. Then,

the

mantissas

are

added algebraically

to

form

an

intermediate sum.

If

an

over-

flow

carry

occurs,

the

intermediate

sum

is right-shifted one digit

and

its

exponent is increased by one.

If

this

causes

an

overflow,

an

exponent overflow

interrupt

condition occurs.

For

short

operands,

the

intermediate sum consists of seven hexa-

decimal digits

and

a possible carry. The low-order

digit

is

the

guard

digit which is retained

from

the

mantissa which is shifted

right.

Only one

guard

digit participates in

the

mantissa

addition. The

guard

digit is zero

if

no

shift

occurs.

210

Loading...

Loading...