DIRECT

CONTROL

INTERFACE

Static Out

Lines

Static

In

Lines

Signal Out Line

External

Signal

In

Line

Power Failure

Line

(PFNOJ

Power Failure Inhibit

In

Line

(PFIR)

Multi-Processor Installation

• The Director Control interface connects

from

two to six processors into

a multi-processor complex.

Each

of

the

processors can have up to six

direct

control

trunks

which contain

the

signal lines

that

transmit

and

receive

the

direct

control information. These signal lines function

as

follows:

• The

Static

Out lines

are

logically identical (common) on all

trunks

(information

on one

trunk

is identical to information

of

all

other

trunks).

The

state

of

these

Static

Out

lines is established when a

Write

Direct

instruction is executed

and

remains

static

until altered by a subsequent

Write

Direct instruction.

Parity

is not generated

or

checked on these lines.

(See

Write

Direct instruction.)

• The

Static

In

lines provide

the

means

for

the receiving processor to

receive 8-bit bytes

of

data

from

other

transmitting

processors via

their

Static

Out lines.

Each

trunk

may

be uniquely sampled

by

a Read

Direct

instruction

which specifies

the

desired

trunk.

(See Read

Direct

instruction.)

•

The

Signal Out line provides a signal to

the

other

processors upon

execution

of

a

Write

Direct instruction. The

Direct

Control

Trunks

(DCT)

whose Signal

Out lines

are

signaled is specified by

the

I-Field

pattern

of

the

instruction.

• The

External

Signal

In

line provides the means

for

receiving a signal

from

other

processors via

their

Signal

Out

lines. The

External

Signal

In

line is logically connected to

the

external

signal

interrupt

flag associated

with

each Direct Control

Trunk

(DCT)

as

indicated:

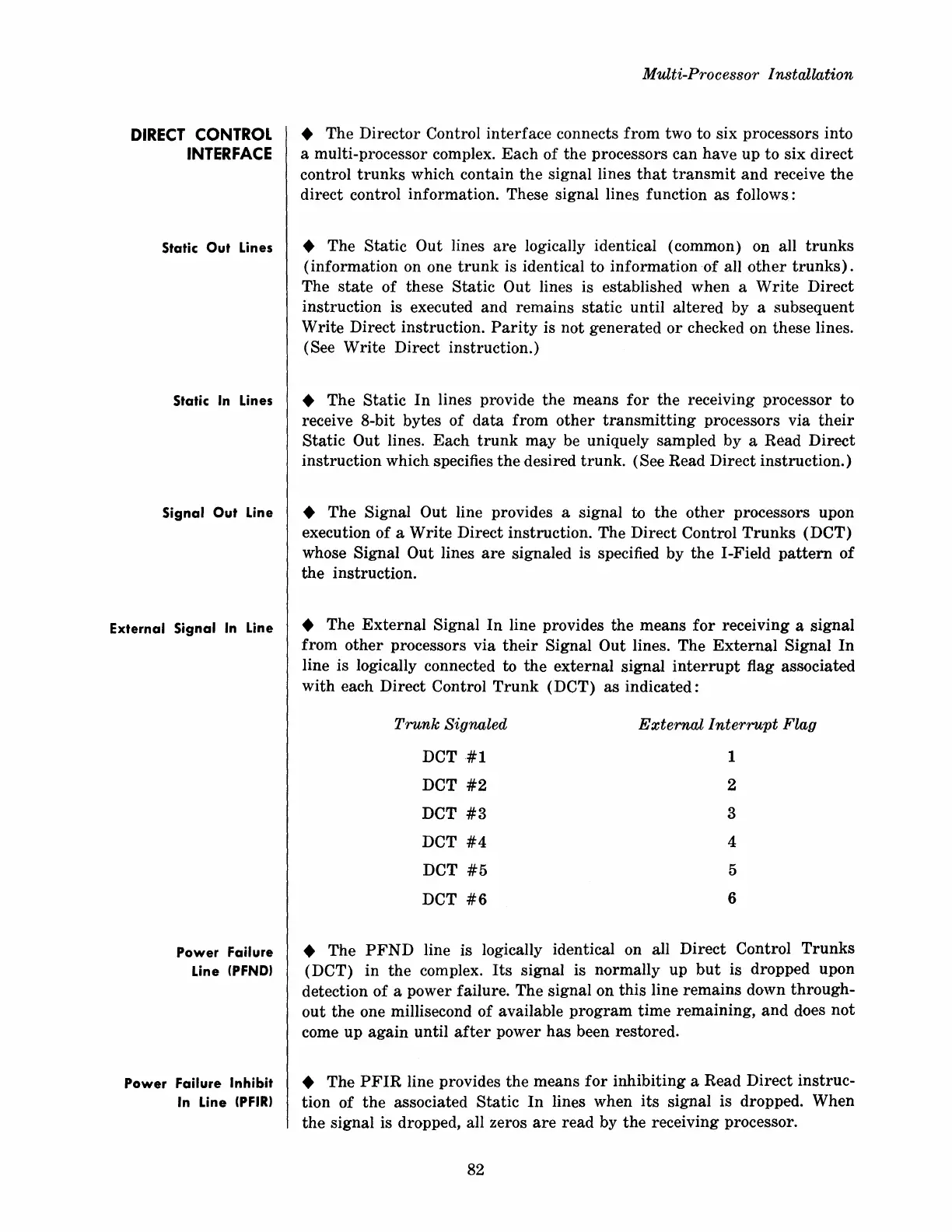

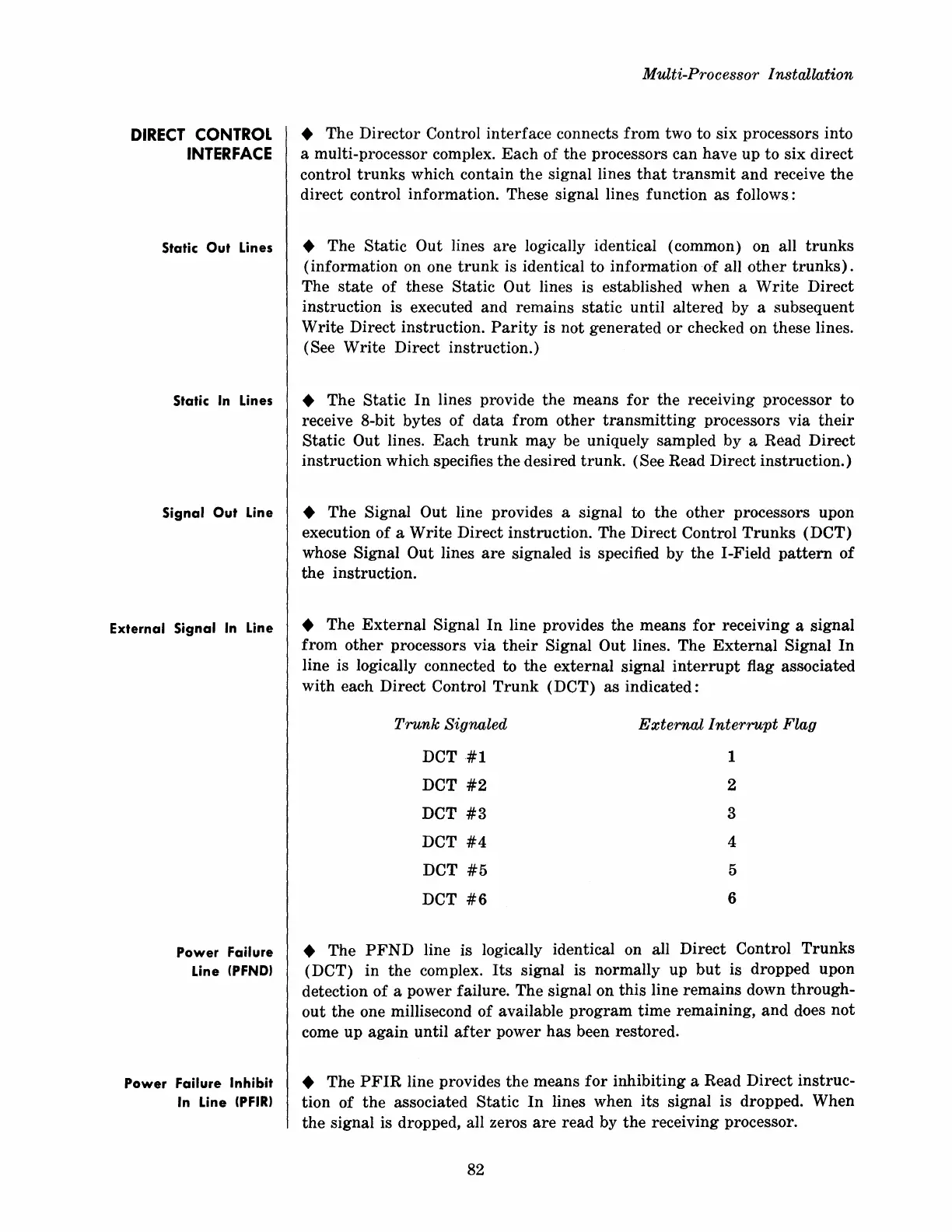

Trunk Signaled

External Interrupt Flag

DCT#l

1

DCT

#2

2

DCT

#3

3

DCT

#4

4

DCT

#5

5

DCT

#6

6

• The

PFND

line is logically identical on all

Direct

Control

Trunks

(DCT)

in

the

complex.

Its

signal is normally up

but

is dropped upon

detection of a power failure. The signal on

this

line

remains

down

through-

out

the

one millisecond

of

available

program

time remaining,

and

does

not

come up

again

until

after

power

has

been restored.

• The

PFIR

line provides

the

means

for

inhibiting

a Read

Direct

instruc-

tion

of

the

associated

Static

In

lines when

its

signal is dropped. When

the

signal is dropped, all zeros

are

read

by

the

receiving processor.

82

Loading...

Loading...