MEMORY

ADDRESS

TRANSLATION

(Cont'd)

Addressing

2. 70/45 Mode (non-translate): Memory is addressed directly

using

the

addresses

generated

during

staticizing. The

70/45

mode is used

by

all

programs

other

than

70/46

programs.

In

the

70/46

mode each memory address, except

I/O

instruction

execu-

tion

and

servicing,

may

be

transl~ted.

The

addresses ( called

virtual

addresses)

of

instructions,

taken

from

the

next

instruction

address

field

of

the

P-counter,

and

data

operands

may

be

translated

via a

table

look-up

to

obtain

actual

memory addresses.

Virtual

addresses consist

of

24

bits

using

the

following

format:

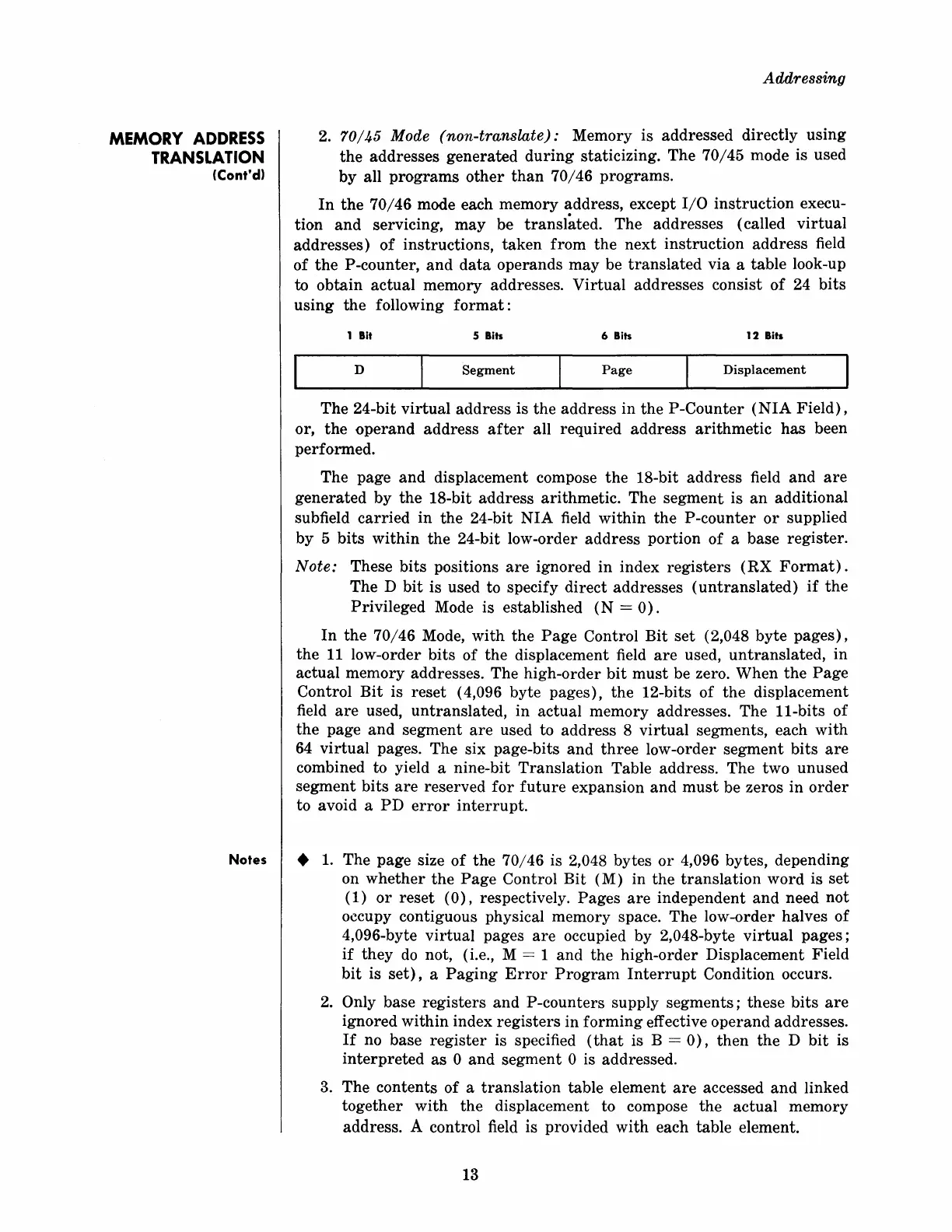

1 Bit 5 Bits 6 Bits

12

Bits

D

Segment

Page

Displacement

The

24-bit

virtual

address

is

the

address

in

the

P-Counter

(NIA

Field),

or,

the

operand

address

after

all

required

address

arithmetic

has

been

performed.

The page

and

displacement compose

the

18-bit

address

field

and

are

generated

by

the

18-bit

address

arithmetic. The

segment

is

an

additional

subfield

carried

in

the

24-bit

NIA

field

within

the

P-counter

or

supplied

by

5

bits

within

the

24-bit low-order

address

portion

of

a base register.

Note: These

bits

positions

are

ignored

in

index

registers

(RX

Format).

The

D

bit

is used to specify

direct

addresses

(untranslated)

if

the

Privileged Mode is established

(N

=

0).

In

the

70/46

Mode,

with

the

Page

Control

Bit

set

(2,048

byte

pages),

the

11

low-order

bits

of

the

displacement field

are

used,

untranslated,

in

actual memory addresses. The high-order

bit

must

be zero. When

the

Page

Control

Bit

is reset (4,096 byte

pages),

the

12-bits

of

the

displacement

field

are

used,

untranslated,

in

actual memory addresses. The 11-bits of

the

page

and

segment

are

used to

address

8

virtual

segments, each

with

64

virtual

pages. The six page-bits

and

three

low-order

segment

bits

are

combined to yield a nine-bit

Translation

Table address. The two unused

segment

bits

are

reserved

for

future

expansion

and

must

be zeros

in

order

to avoid a

PD

error

interrupt.

Notes

•

1.

The page size

of

the

70/46

is 2,048 bytes

or

4,096 bytes, depending

on

whether

the

Page

Control

Bit

(M) in

the

translation

word

is

set

(1)

or

reset

(0),

respectively.

Pages

are

independent

and

need

not

occupy contiguous physical memory space.

The

low-order halves

of

4,096-byte

virtual

pages

are

occupied by 2,048-byte

virtual

pages;

if

they

do

not, (i.e., M = 1

and

the

high-order

Displacement Field

bit

is

set),

a

Paging

Error

Program

Interrupt

Condition occurs.

2.

Only base

registers

and

P-counters supply

segments;

these

bits

are

ignored

within

index

registers

in

forming

effective

operand

addresses.

If

no base

register

is specified

(that

is B =

0),

then

the

D

bit

is

interpreted

as

0

and

segment 0 is addressed.

3.

The

contents

of

a

translation

table element

are

accessed

and

linked

together

with

the

displacement to compose

the

actual

memory

address.

A control field is provided

with

each table element.

13

Loading...

Loading...