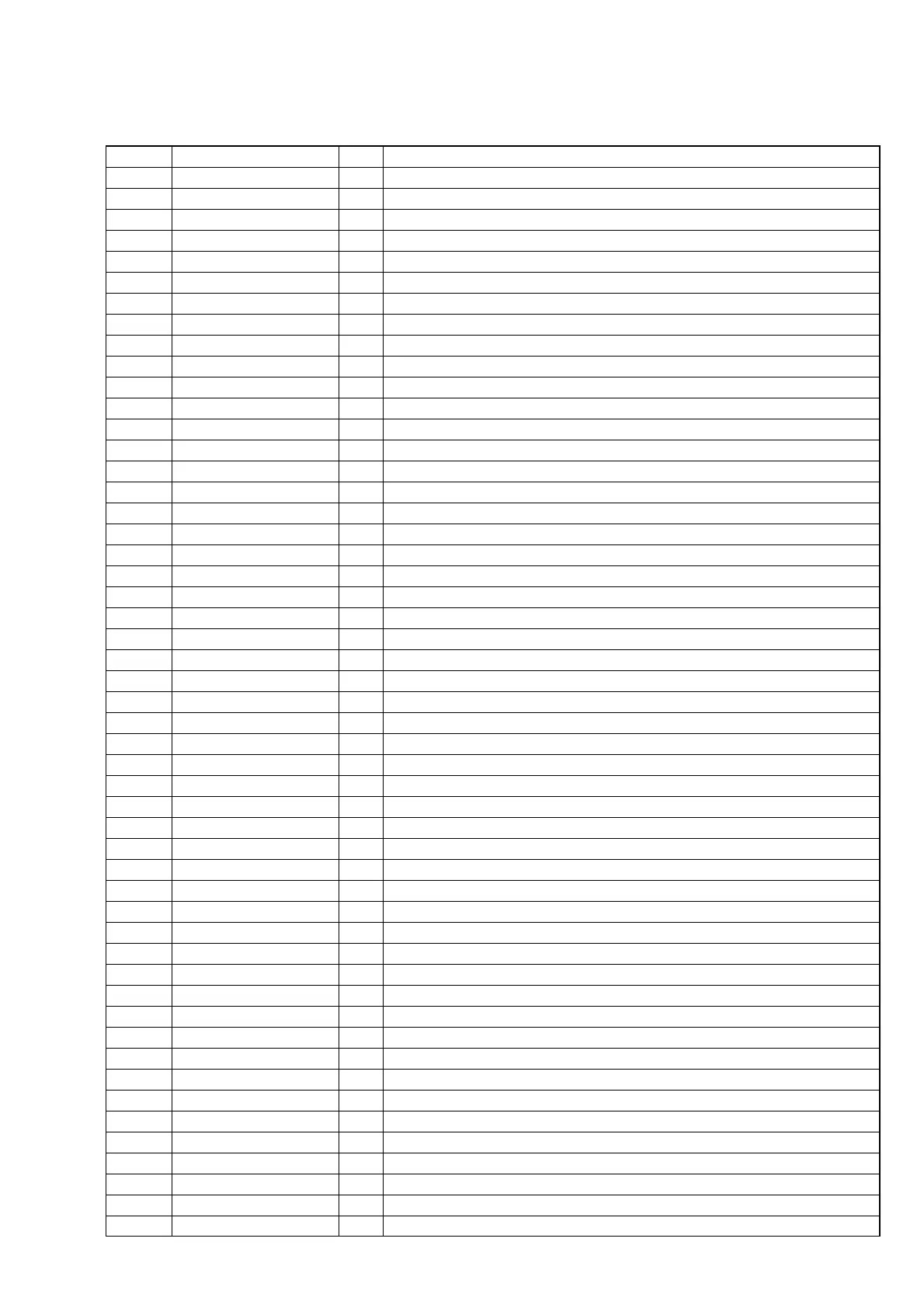

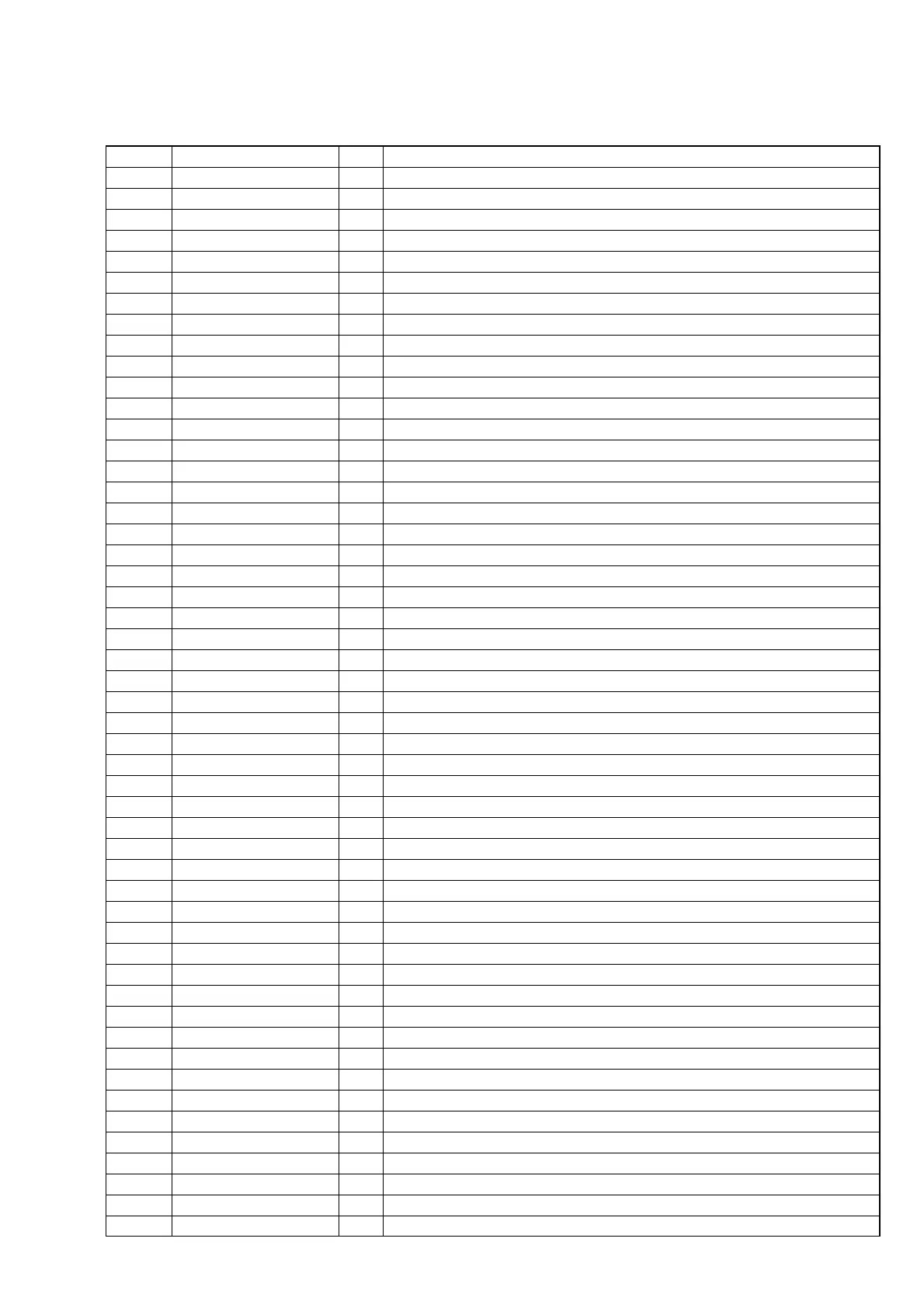

13

STR-DE685

SECTION 4

DIAGRAMS

1 VSS — Ground

2 XRST I Reset signal input

3 EXTIN I Not used (connected to ground)

4 FS2 I Not used (connected to ground)

5 VDDI I Power supply

6 FS1 I Not used (connected to ground)

7 PLOCK O Internal PLL lock signal output (Not used)

8 VSS — Ground

9 MCLK1 I Clock signal input (13.5 MHz)

10 VDDI I Power supply

11 VSS — Ground

12 MCLK2 O Clock signal output (13.5 MHz)

13 MS I Switching of master/slave operation L : internal clock, H : EXTIN clock is used

14 SCKOUT O Internal system clock signal output

15 LRCKI1 I Not used (open)

16 VDDE I Power supply

17 BCKI1 I Not used (open)

18 SDI1 I Audio IF data input

19 LRCKO O Sampling clock output for digital audio serial data

20 BCKO O Bit clock output terminal for digital audio serial data

21 VSS — Ground

22 KFSIO I/O Audio clock signal (364fs/256fs) input/output

23 to 25 SDO1 to SDO3 O Digital audio serial data output

26 SDO4 O Audio IF serial output (Not used) (open)

27 SPDIF O Not used (open)

28 LRCKI2 I Sampling clock input for audio serial data

29 BCKI2 I Bit clock input terminal for audio serial data

30 SDI2 I Digital audio data input

31 VSS — Ground

32 HACN O Acknowledge signal output for system control

33 HDIN I Serial data input for system control

34 HCLK I Clock input for system control

35 HDOUT O Serial data output for system control

36 HCS I Chip select input for system control

37 SDCLK O Not used (open)

38 CLKEN O Not used (open)

39 RAS O Not used (open)

40 VDDI I Power supply

41 VSS — Ground

42 CAS O Not used (open)

43 DQM/OE0 O Not used (open)

44 CS0 O External memory chip select (SRAM)

45 WE0 O SRAM write enable output

46 VDDE I Power supply

47 WMD1 I Not used (connected to “H”)

48 VSS — Ground

49 WIMD0 I Not used (connected to ground)

50 PAGE2 O Not used (open)

51 VSS — Ground

52 PAGE1 O External memory page switching signal output (Not used)

53 PAGE0 O External memory page switching signal output (Not used)

4-1. IC PIN DESCRIPTIONS

• IC1201 CXD9617R (DSP) (DIGITAL Board (1/2))

Pin No. Pin Name I/O Description

Loading...

Loading...