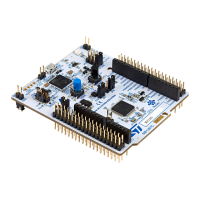

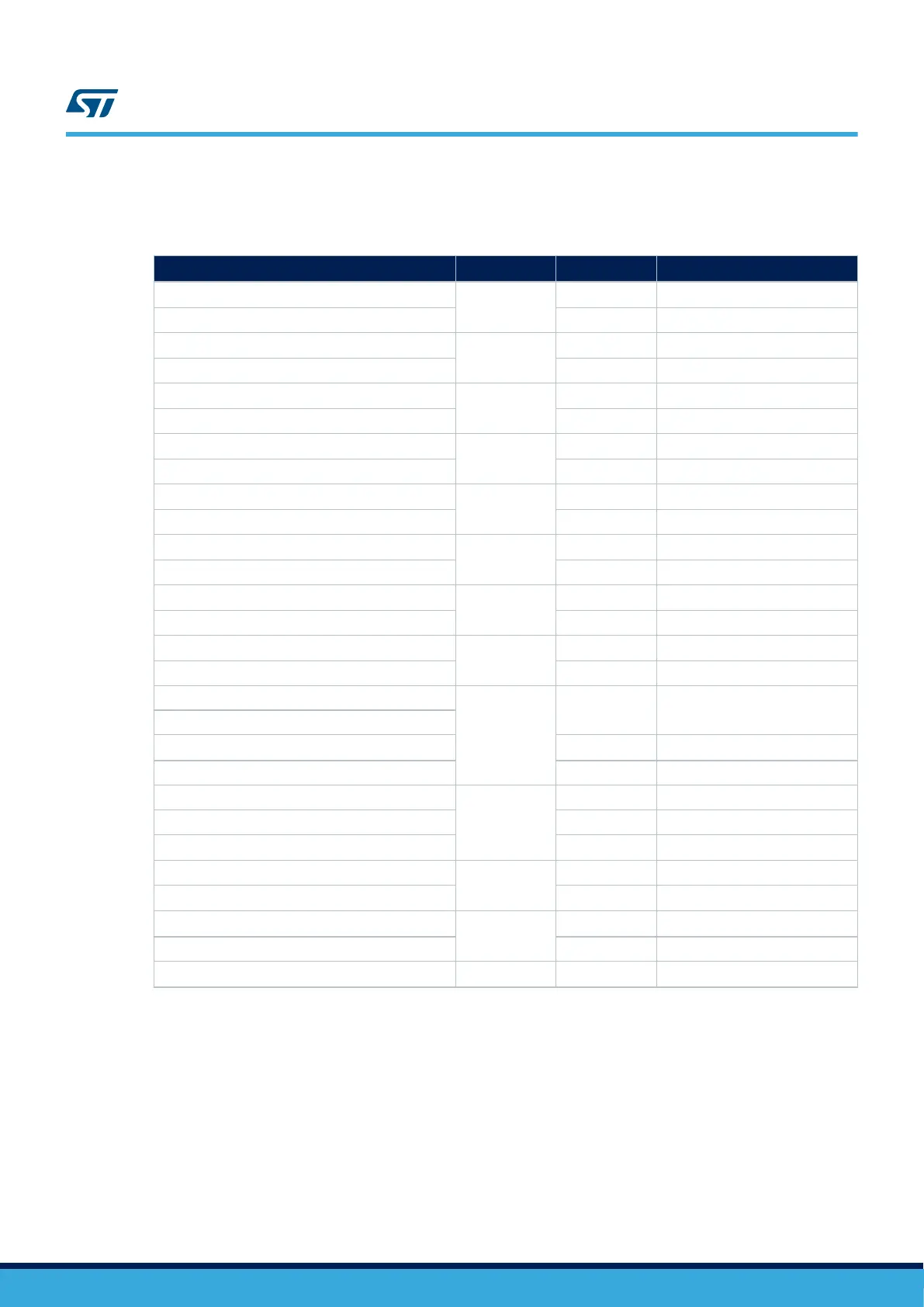

Hardware modifications are listed in Table 56 below:

Table 56. OCSPI2 hardware configuration

Signal name Pin name Setting

OCSPI2

(1)

FMC_A0

PF0

R339

OFF

(2)

OCSPI2_IO0 R98 ON

FMC_A1

PF1

R335

OFF

(2)

OCSPI2_IO1 R89 ON

FMC_A2

PF2

R331

OFF

(2)

OCSPI2_IO2 R82 ON

FMC_A3

PF3

R74

OFF

(2)

OCSPI2_IO3 R75 ON

FMC_A10

PG0

R73

OFF

(2)

OCSPI2_IO4 R76 ON

FMC_A11

PG1

R333

OFF

(2)

OCSPI2_IO5 R77 ON

FMC_A4

PF4

R66

OFF

(2)

OCSPI2_CLK R319 ON

FMC_A5

PF5

R65

OFF

(2)

OCSPI2_NCLK R318 ON

FMC_NE3

PG10

(3)

JP2 OFF

SDIO2_D1

DCMI_D2 R118

OFF

(2)

OCSPI2_IO6 R115 ON

SDIO2_D2

PG11

(3)

JP1 OFF

DCMI_D3 JP1 OFF

OCSPI2_IO7

(2)

R257 ON

SDIO2_D3

PG12

(3)

JP13 OFF

OCSPI2_NCS

(2)

R287 ON

FMC_SDNCAS

PG15

R352

OFF

(2)

OCSPI2_DQS R354 ON

3V3_SW_ENABLE

MFX IO0

(3)

SB34 ON

1. The default configuration is in bold.

2. Remove to avoid stub if necessary.

3. PG10, PG11, PG12 signals are using pins supplied by VDDMMC. Make sure to supply 3.3 V on VDDMMC (Refer to Section

6.3.5 )

UM2662

OCSPI NOR Flash 2 module (MB1242)

UM2662 - Rev 1

page 59/95

Loading...

Loading...