Platform Cable USB II

DS593 (v1.2.1) March 17, 2011 www.xilinx.com

16

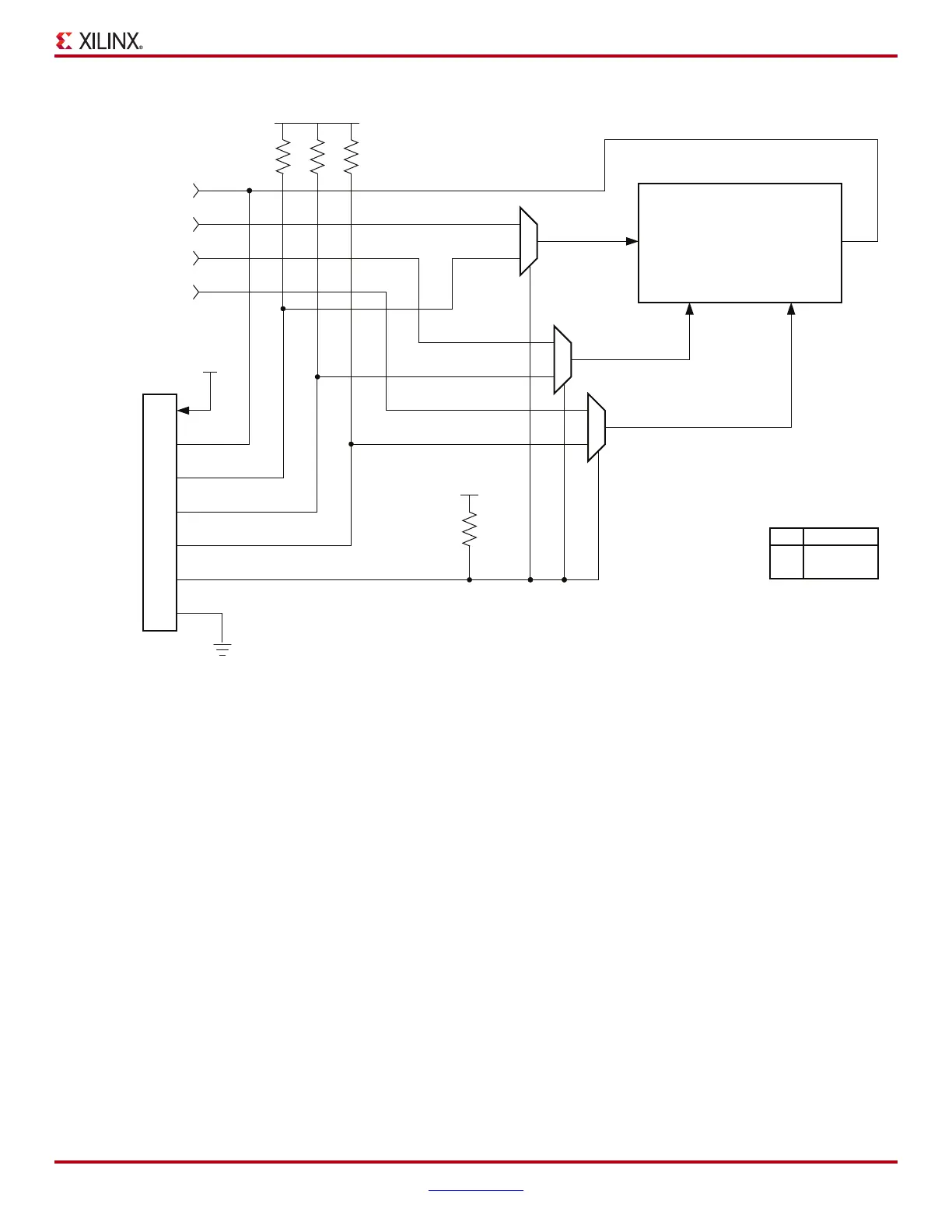

X-Ref Target - Figure 16

Notes:

1. Example implies that V

CCO

, V

CCJ

, and/or V

CCAUX

for various devices in the JTAG chain are set to the same voltage.

2. Attach the following 2-mm connector pins to digital ground: 3, 5, 7, 9, and 11.

3. The cable uses an open-drain driver to control the pseudo ground (PGND) signal — an external pull-up resistor is required.

4. Assumes that the multiplexor supply voltages pins are connected to V

CCAUX

.

5. Pin 13 is grounded on legacy Xilinx USB cables (models DLC9, DLC9G and DLC9LP), and Parallel Cable IV (model DLC7). These cables

need to be manually detached from the 2-mm connector to allow the primary configuration source to have access to the JTAG chain.

Figure 16: Example Using PGND in a JTAG Chain

8

2

10

4

6

13

*

V

REF

TDO

TDI

TMS

TCK

PGND

(5)

GND

(2)

JTAG CHAIN

TDI TDO

TMS TCK

TMS

TDI

TDO

TCK

A

B

S

Y

MUX Truth Table

S Output

HY = A

LY = B

A

B

S

Y

A

B

Y

S

Configuration Source

(Primary)

2-mm

Connector

Platform Cable USB II

(Secondary)

V

CCAUX

(1)

1 KΩ

Required

Pull-Up

(3)

DS593_16_021408

(4)

(4)

(4)

10 KΩ

V

CCAUX

10 KΩ

10 KΩ

V

CCAUX

Loading...

Loading...