ConnectCore for i.MX51

©2011DigiInternational,Inc. 12

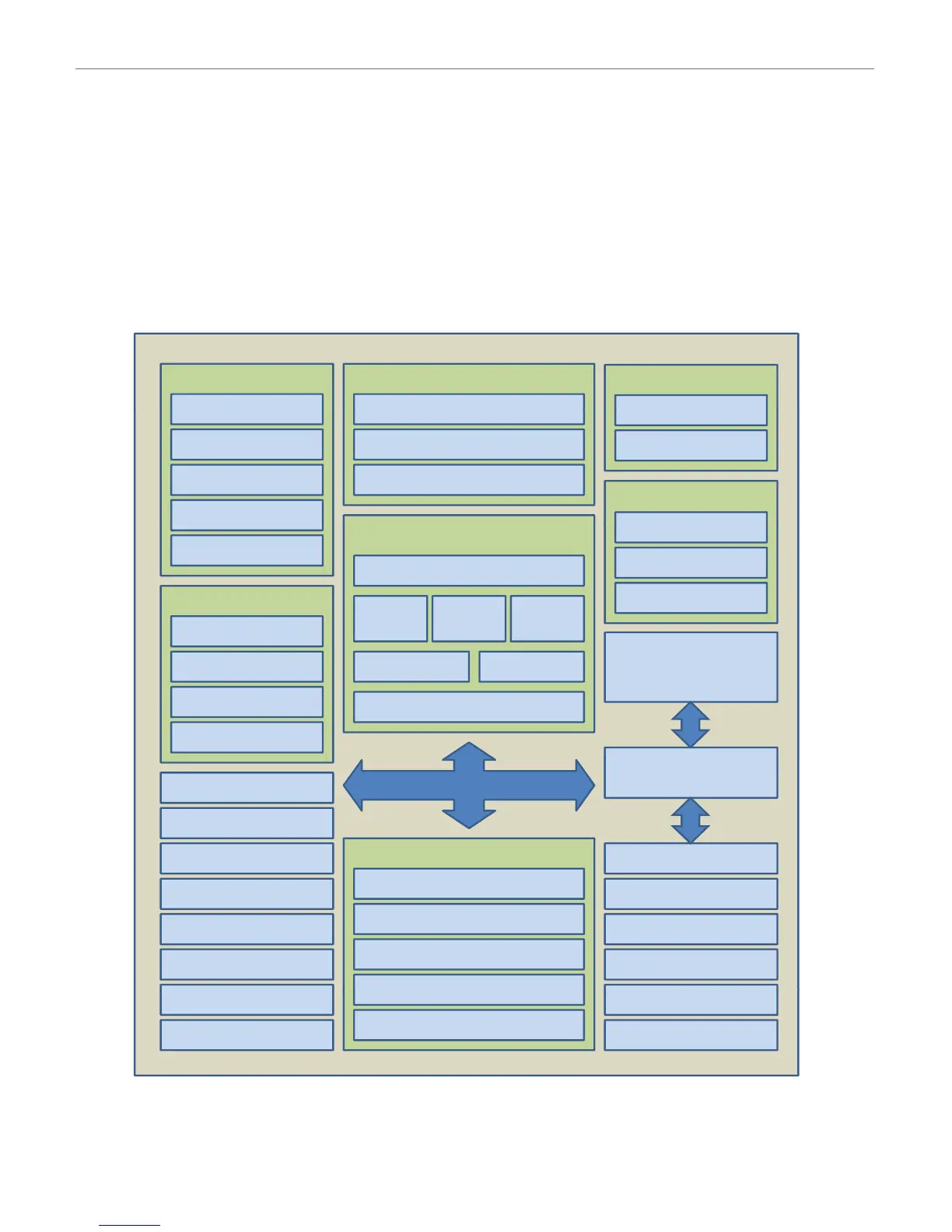

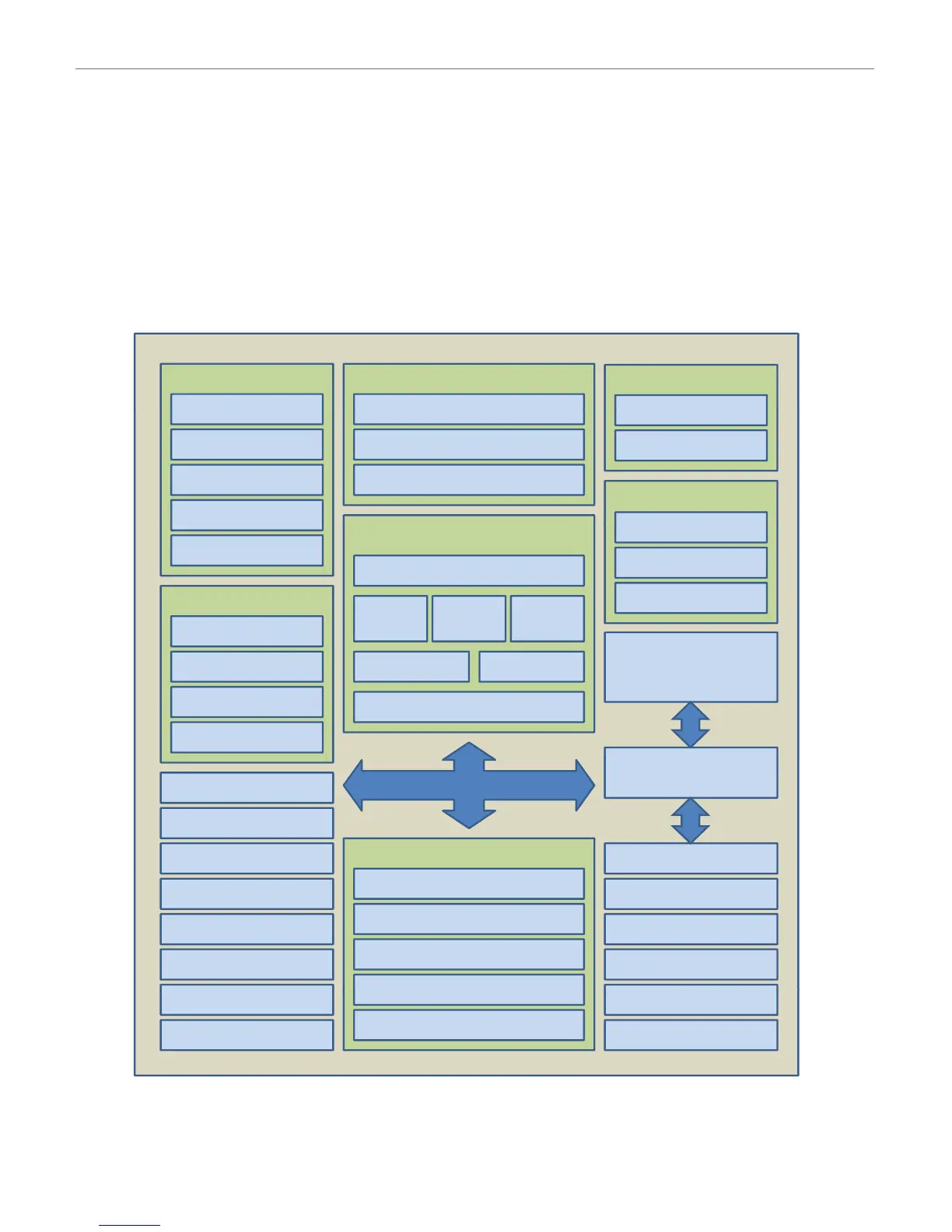

Block Diagram

The next figures show the block diagram of the Freescale i.MX515 CPU and the block diagram

of the ConnectCore for i.MX51 module.

CPU

HW Video Codecs

HD720 TV-Out

SRTC

Syste Control

Secure JTAG

ore

600/800 Cortex-A8

32KB

I-Cache

32KB

D-Cache

256KB

L2-Cache

Power Mgmt

PLL x 3

Clock Reset

Neon

Vector Floag Point Unit

ETM

External Memory

Interface

Processin Unit

Fast IrDA

1-Wire

I

2

C x 2 HS MMC /SDIO x 4

Smart DMA

/AHBSwitch Fric

Dual-Display Controller

Image Signal Processor

Resizing & Blending

GPIO

Keypad

USB OTG Host + PHY

SSI/I2S x 3

UART x 3

CSPI HS x 2 / LS x 1

Dual-Camera Interface

USB Host x 3

Fuse Box

SPDIF Tx

10/100 Ethernet x

WatchDog x 2

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...