Appendices

A-18

CP2E CPU Unit Software User’s Manual(W614)

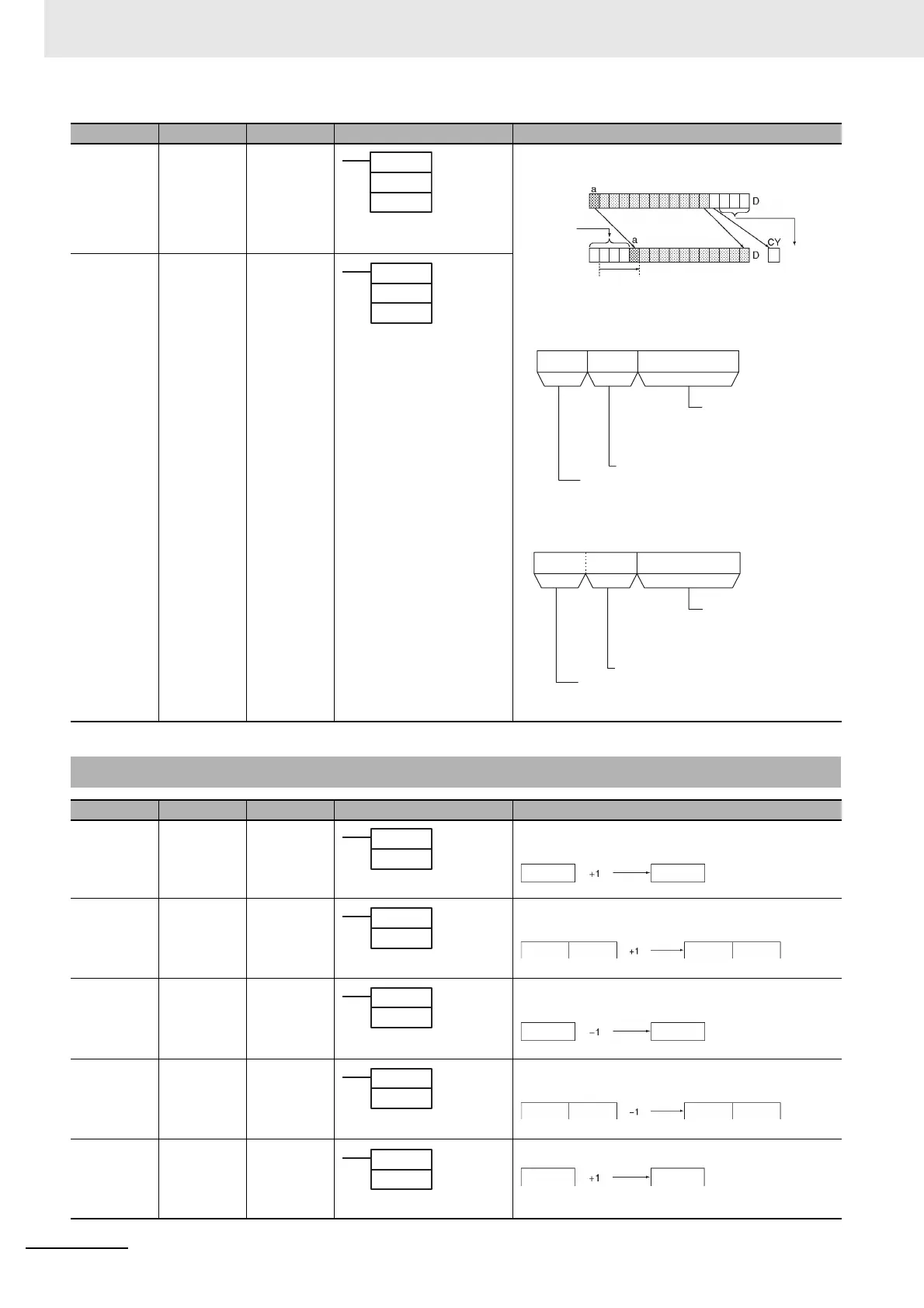

SHIFT N-BITS

RIGHT

NASR @ Shifts the specified 16 bits(NASR) or 32 bits(NSRL) of word data

to the right by the specified number of bits.

C: Control word

• NASR

• NSRL

DOUBLE

SHIFT N-BITS

RIGHT

NSRL @

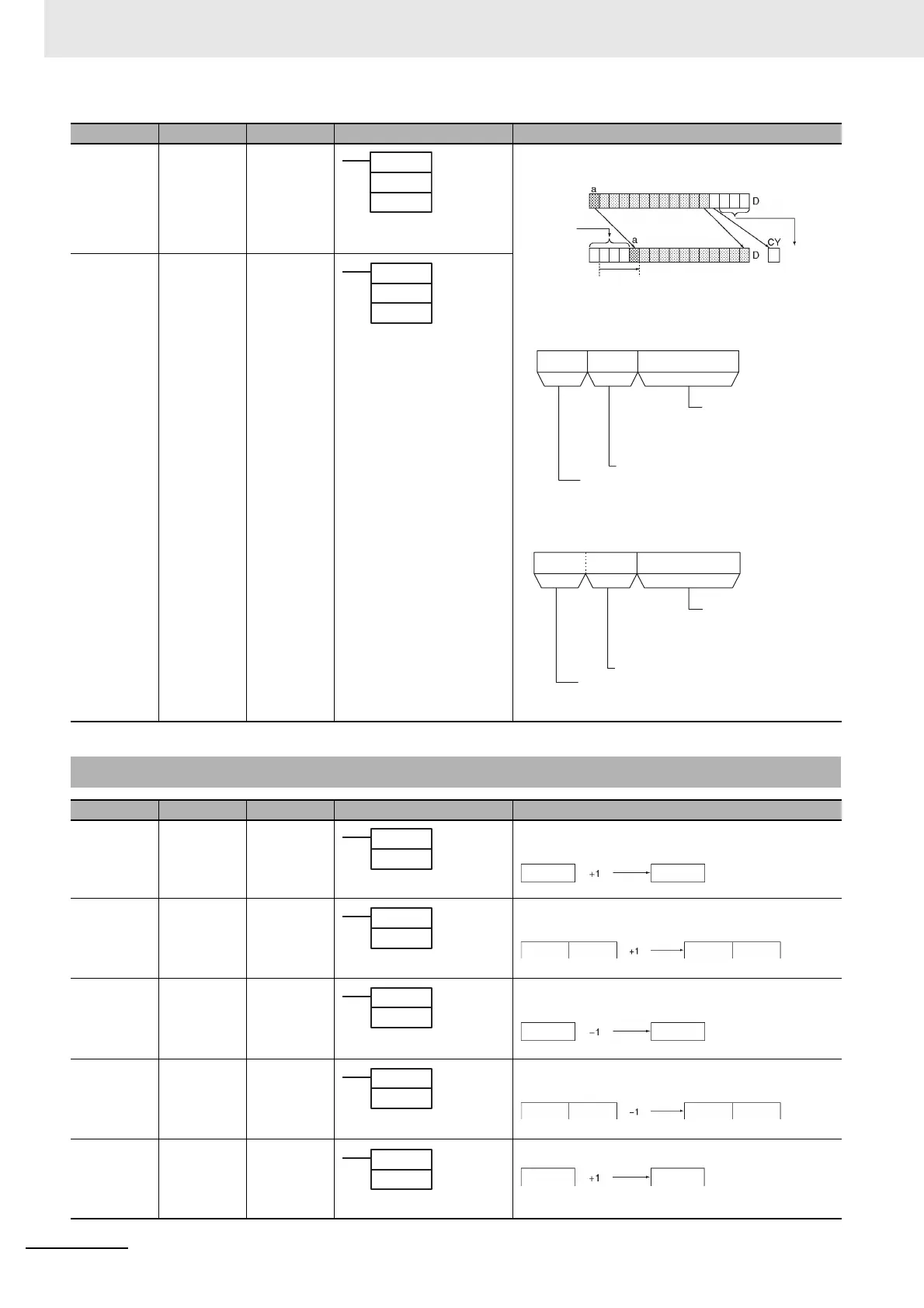

A-1-8 Increment/Decrement Instructions

Instruction Mnemonic Variations Symbol/Operand Function

INCREMENT

BINARY

++ @ Increments the 4-digit hexadecimal content of the specified word

by 1.

DOUBLE

INCREMENT

BINARY

++L @ Increments the 8-digit hexadecimal content of the specified words

by 1.

DECREMENT

BINARY

− − @ Decrements the 4-digit hexadecimal content of the specified word

by 1.

DOUBLE DEC-

REMENT

BINARY

− −L @ Decrements the 8-digit hexadecimal content of the specified

words by 1.

INCREMENT

BCD

++B @ Increments the 4-digit BCD content of the specified word by 1.

Instruction Mnemonic Variations Symbol/Operand Function

NASR(581)

D

C

D: Shift word

C: Control word

Lost

N bits

Contents of

"a" or "0"

shifted in

15 8 011 712

C

0

No. of bits to shift: 00 to 10 Hex

Always 0.

Data shifted into register

0 Hex: 0 shifted in

8 Hex: Contents of rightmost bit shifted in

15 8 011 712

C

0

No. of bits to shift: 00 to 20 Hex

Always 0.

Data shifted into register

0 Hex: 0 shifted in

8 Hex: Contents of rightmost bit shifted in

NSRL(583)

D

C

D: Shift word

C: Control word

++(590)

Wd

Wd: Word

Wd Wd

++L(591)

Wd

Wd: Word

Wd+1 Wd Wd+1 Wd

− − (592)

Wd

Wd: Word

Wd Wd

− − L(593)

Wd

Wd: 1st word

Wd+1 Wd Wd+1 Wd

++B(594)

Wd

Wd: Word

Wd Wd

Loading...

Loading...