RZ Family / RZ/G, RZ/A Series 2. Functional Specifications

R01UH0990EJ0101 Rev.1.01 Page 46 of 83

Jul 28, 2022

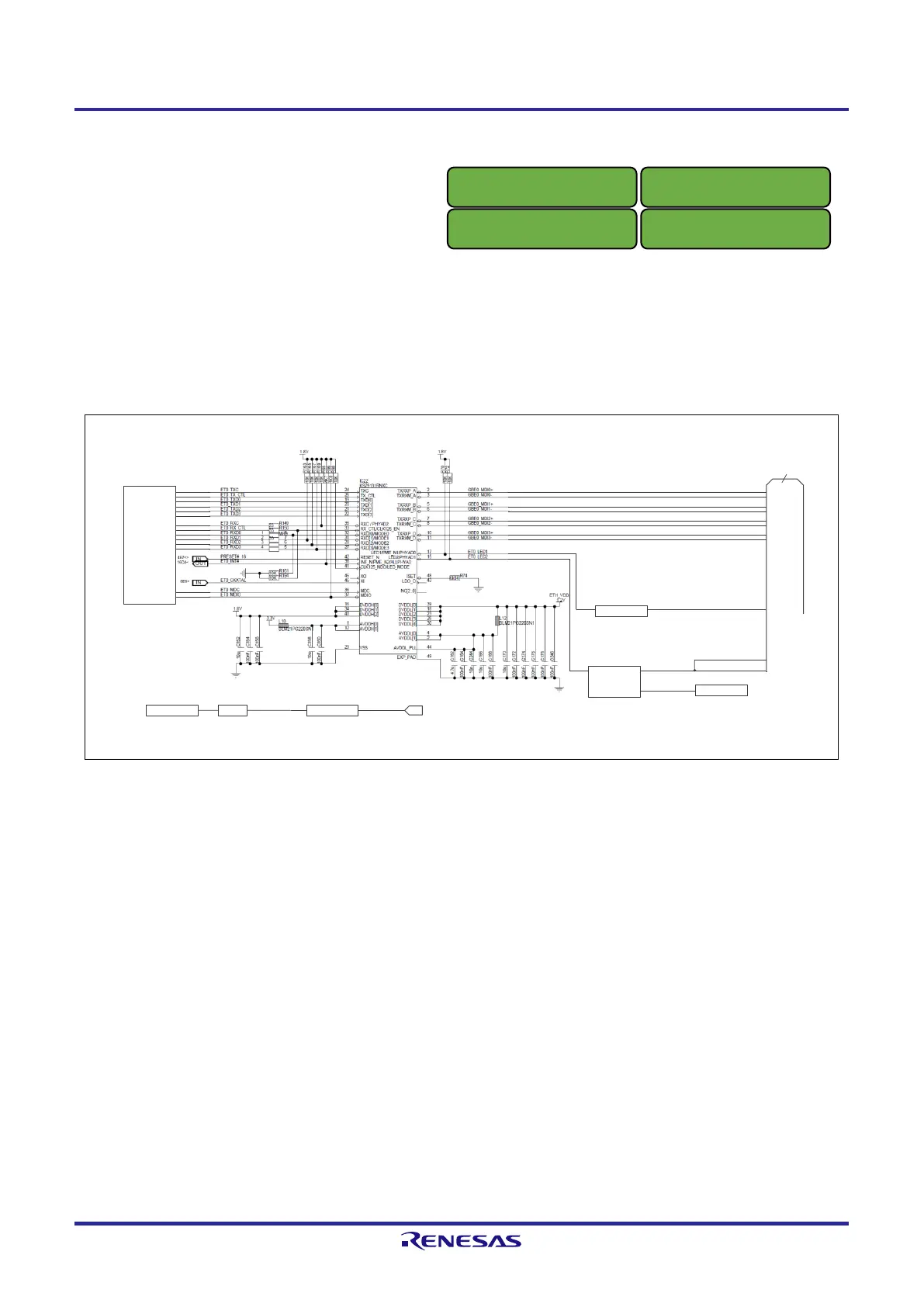

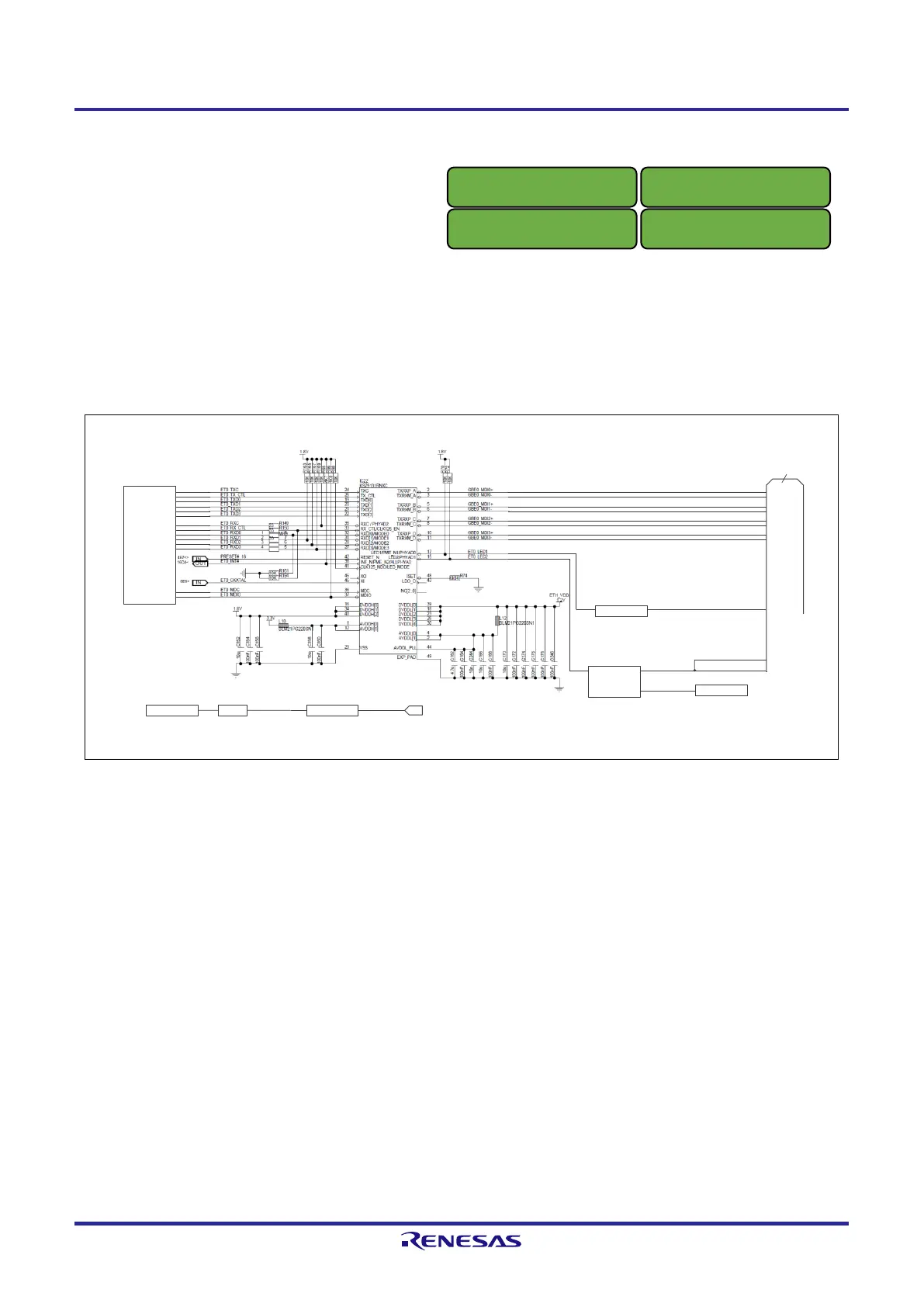

2.4 Gigabit Ethernet Interface

Figure 2.4 and Figure 2.5 show a block diagram of Gigabit Ethernet0 and Ethernet1 interface.

The Gigabit Ethernet Interface is controlled by the Ethernet controller (E-MAC) hat conforms to the definition of the

MAC (Media Access Control) layer that is with built-in to the RZ/G2UL. The Ethernet clock is sourced from a clock

generator connected to the Ethernet PHY.

This interface complies with IEEE802.3 PHY RGMII.

Figure 2.4 Block Diagram of Gigabit Ethernet0 I/F

ET0_TXC/TX_CLK

ET0_TX_CTL/TX_EN

ET0_TXD0

ET0_TXD1

ET0_TXD2

ET0_TXD3

ET0_RXC/RX_CLK

ET0_RX_CTL/RX_DV

ET0_RXD0

ET0_RXD1

ET0_RXD2

ET0_RXD3

ET0_MDC

ET0_MDIO

11

SMARC Edge Connector

RZ/G2UL, RZ/A3UL, RZ/Five

ET0_LINKSTA

RZ/G2UL, RZ/A3UL, RZ/Five

SLG7RN45356

IO12 IO7

IO13

9

16

15

ET0_LINKSTA

GBE0_LINK_LED

GBE0_LINK100#

GBE0_LINK1000#

SLG7RN45315

IO2 IO4

64 GBE0_LINK_ACT#

SLG7RN45315

IO9 IO0

212 ET0_INT#RZ_IRQ2_ET0_INT#

P5_1

RZ/G2UL, RZ/A3UL, RZ/Five

Level Shifter

IN

Loading...

Loading...