RZ Family / RZ/G, RZ/A Series 2. Functional Specifications

R01UH0990EJ0101 Rev.1.01 Page 55 of 83

Jul 28, 2022

2.11 SD/MMC Host Interface

2.11.1 eMMC Memory

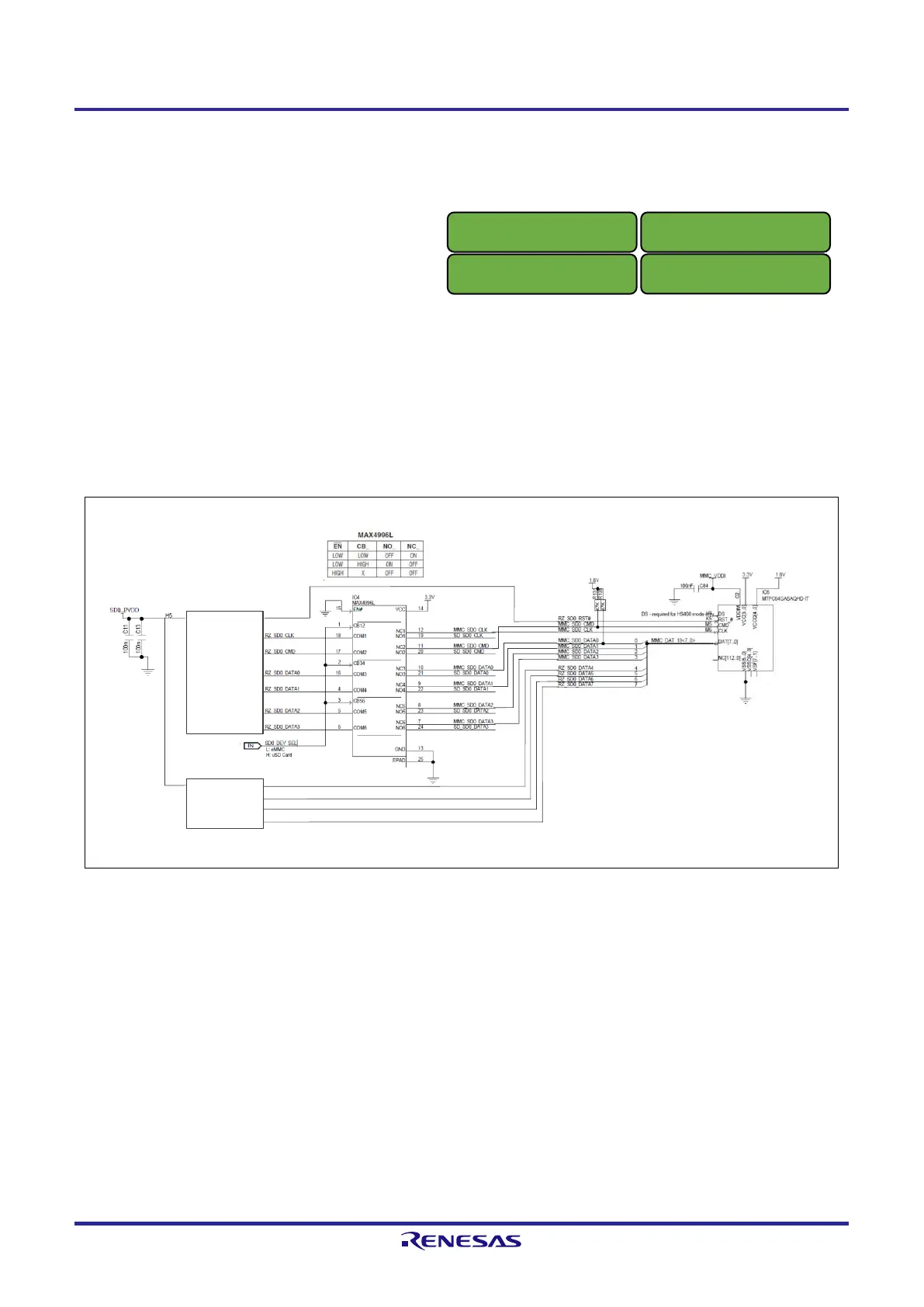

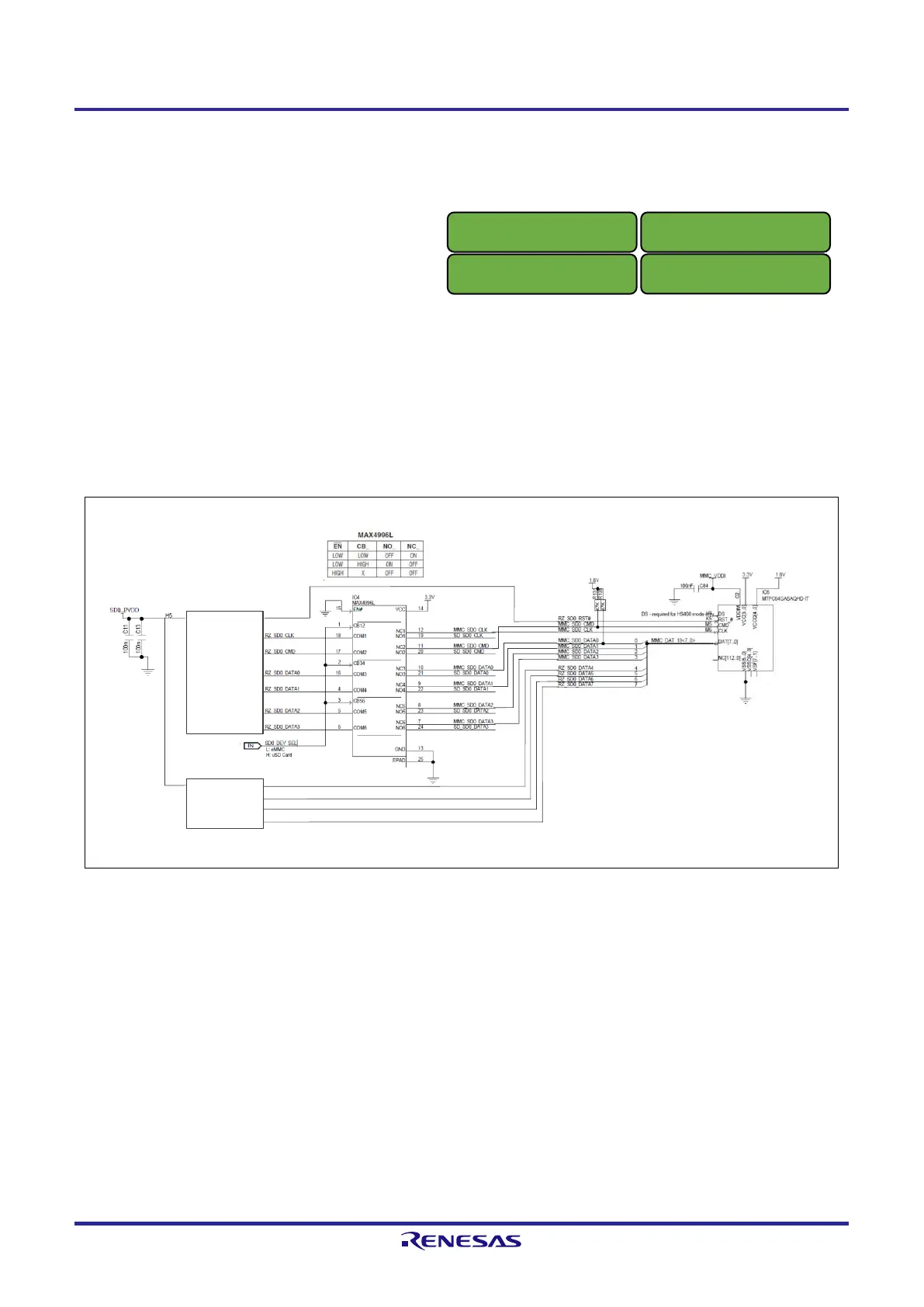

Figure 2.13 shows a block diagram of the MMC interface.

The eMMC memory is connected to channel 0 of SD/MMC interface that is with built-in to the RZ/G2UL. This

memory is used in conjunction with SD card.

The eMMC memory may be used when

●

the SW_SD0_DEV_SEL is enabled (SW1-2: Selection SD/MMC is OFF).

This interface complies with the JEDEC standard version 4.51 and supports HS200 mode.

Figure 2.13 Block Diagram of eMMC I/F

SD0_RST_N

SD0_CLK

SD0_CMD

SD0_DATA0

SD0_DATA1

SD0_DATA2

SD0_DATA3

SD0_PVDD

SD0_PVDD

SD0_DATA4

SD0_DATA5

SD0_DATA6

SD0_DATA7

SD0_PVDD

RZ/G2UL, RZ/A3UL, RZ/Five

RZ/G2UL, RZ/A3UL, RZ/Five

Loading...

Loading...