www.ti.com

J721E EVM Hardware Architecture

41

SPRUIS4A–December 2019–Revised May 2020

Submit Documentation Feedback

Copyright © 2019–2020, Texas Instruments Incorporated

Jacinto7 J721E/DRA829/TDA4VM Evaluation Module (EVM)

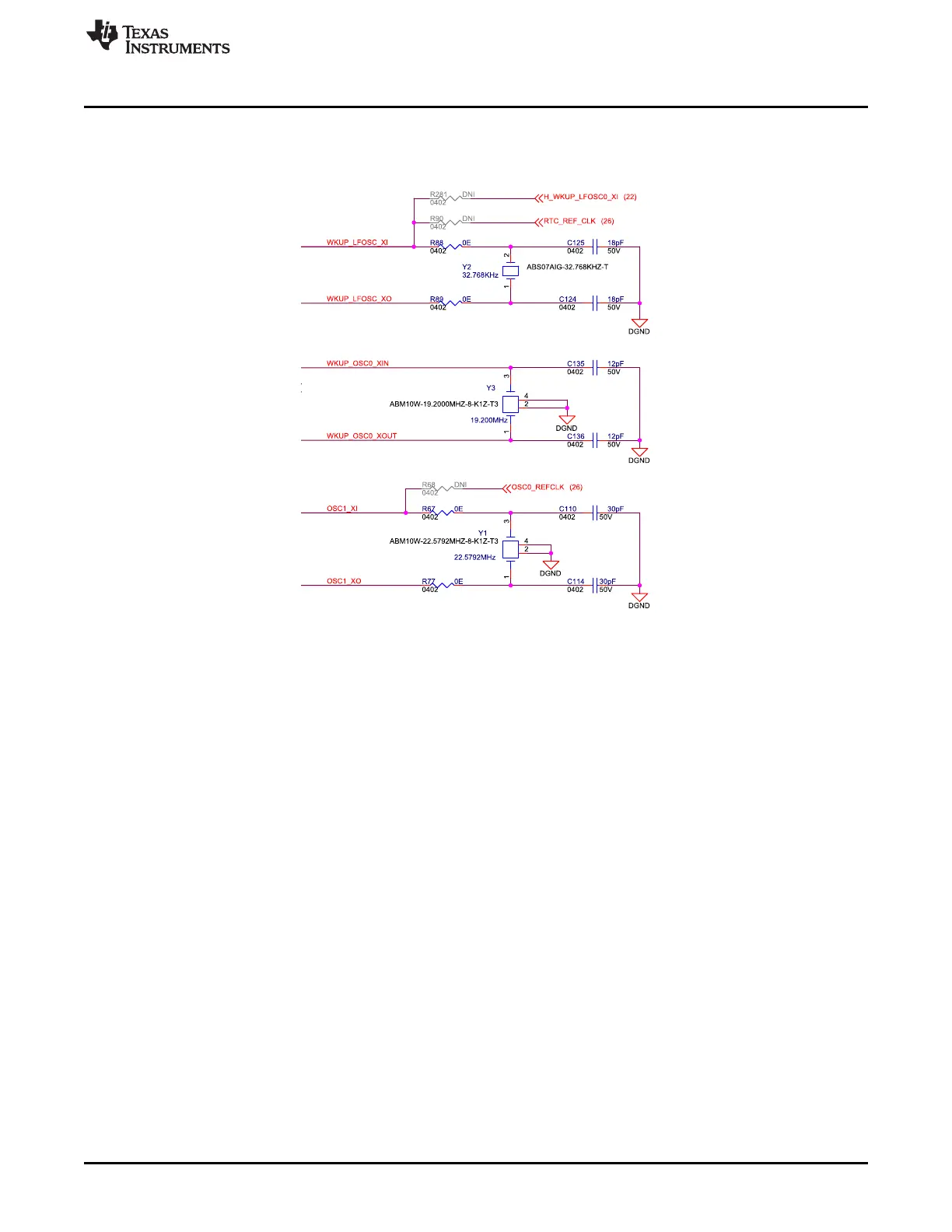

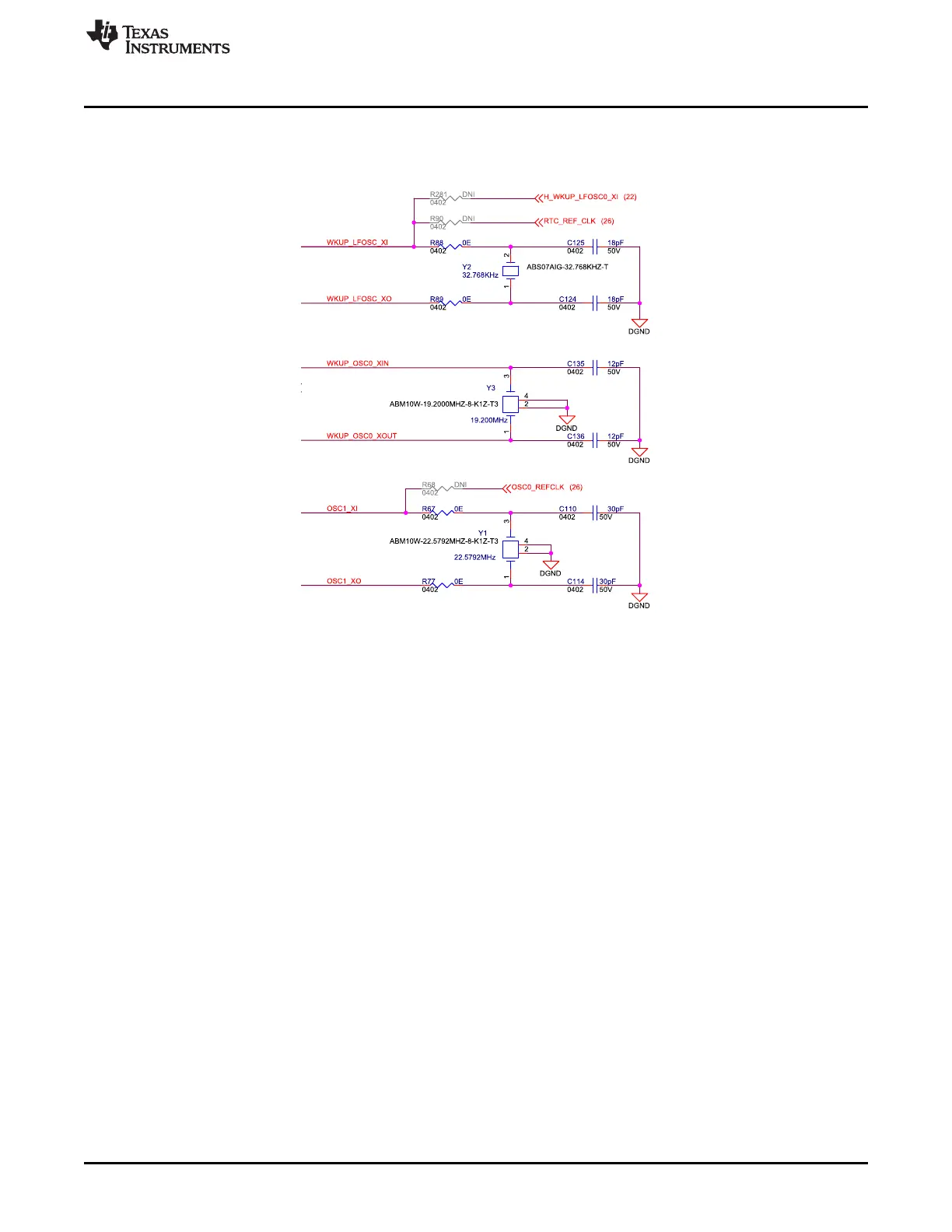

4.7.1 Processor’s Primary Clock

There are three external crystals attached to the J721E processor to provide the SoC’s Primary clocks

WKUP_LFOSC (32 KHz), WKUP_OSC0 (19.2 MHz) and OSC1 (22.5792 MHz) as shown in Figure 24.

Figure 24. J721E SoC Primary Clock

The WKUP_OSC0 is required by the processor. Both WKUP_LFOSC and OSC1 are optional clocks (not

required for J721E processing). The WKUP_LFOSC can be sourced either on the on-board crystal or from

the PMIC. The OSC1 can be sourced from either the on-board crystal or from clock generator

(CDCEL937) on the Common Processor board.

Loading...

Loading...