20 www.xilinx.com Spartan-6 FPGA GTP Transceiver Wizard v1.8

UG546 (v1.8) December 14, 2010

Chapter 3: Running the Wizard

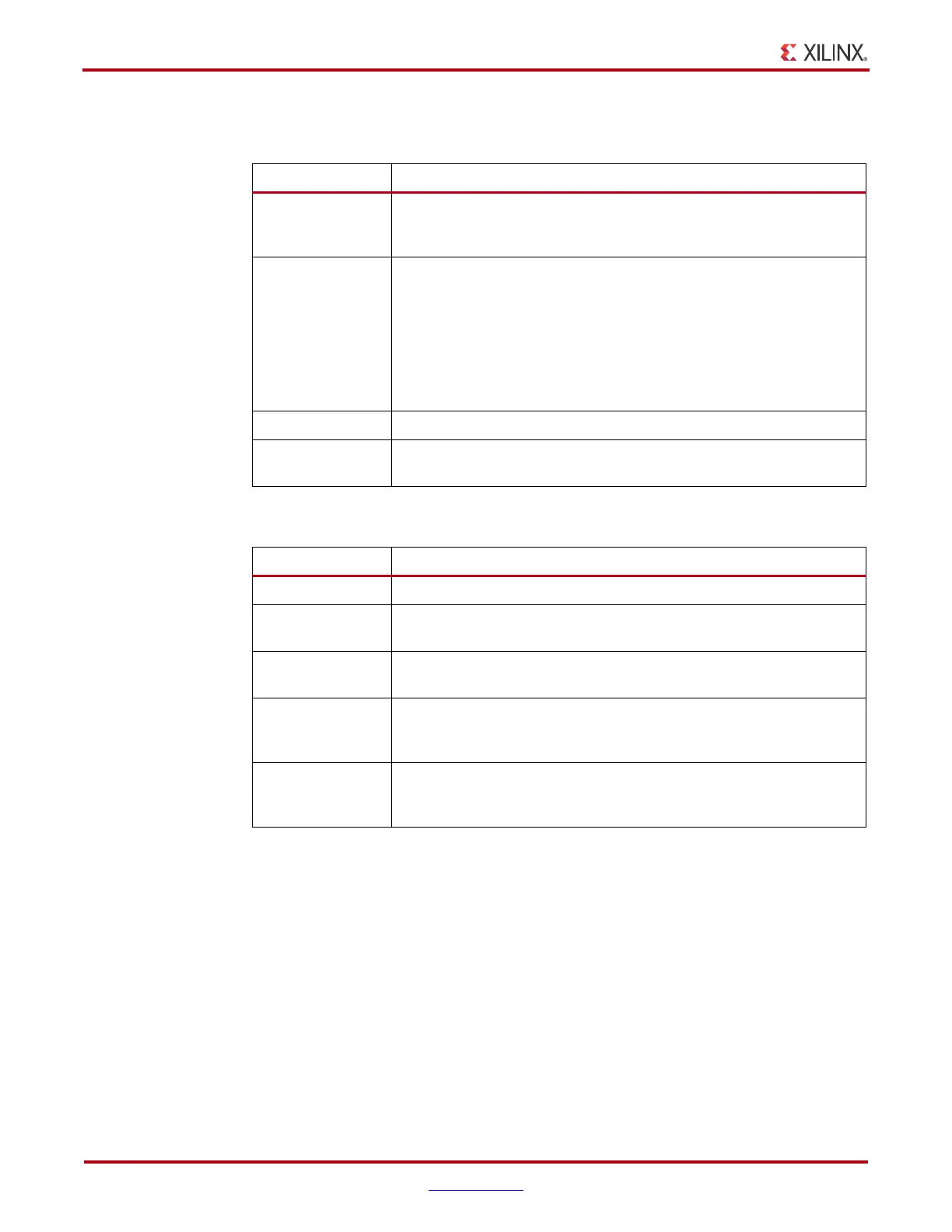

Table 3-1: Select Transceiver and Reference Clocks

Option Description

Tile Location

Select the individual GTPA1_DUAL transceiver pairs by location to be

used in the target design. The PCI EXPRESS example requires one

transceiver pair.

GTP0 REFCLK

Determines the source for the reference clock signal provided to the

GTP0 transceiver in the selected GTPA1_DUAL primitive (see

Table 3-2, page 20). Differential clock signal input pin pairs are

provided for each GTPA1_DUAL. Individual transceivers have access

to the reference clock signals for the two horizontally adjacent

GTPA1_DUAL primitives allowing two primitives to share a single

reference clock signal. The PCI EXPRESS example uses the REFCLK

X0Y0 signal from the upper pair of selected primitives.

GTP1 REFCLK Same as above for the GTP1 transceiver.

Advanced

Clocking

Use this check box to bring out all possible reference clock ports to the

generated wrapper.

Table 3-2: Reference Clock Source Options

Option Description

GREFCLK Reference clock driven by internal fabric. Lowest performance option.

REFCLK_X0Y0

External GTPA1_DUAL reference clock signal local to first upper

transceiver pair.

REFCLK_X1Y0

External GTPA1_DUAL reference clock signal local to second upper

transceiver pair.

REFCLK_X0Y1

External GTPA1_DUAL reference clock signal local to first lower

transceiver pair. Not available on devices with fewer than four

transceiver pairs.

REFCLK_X1Y1

External GTPA1_DUAL reference clock signal local to second lower

transceiver pair. Not available on devices with fewer than four

transceiver pairs.