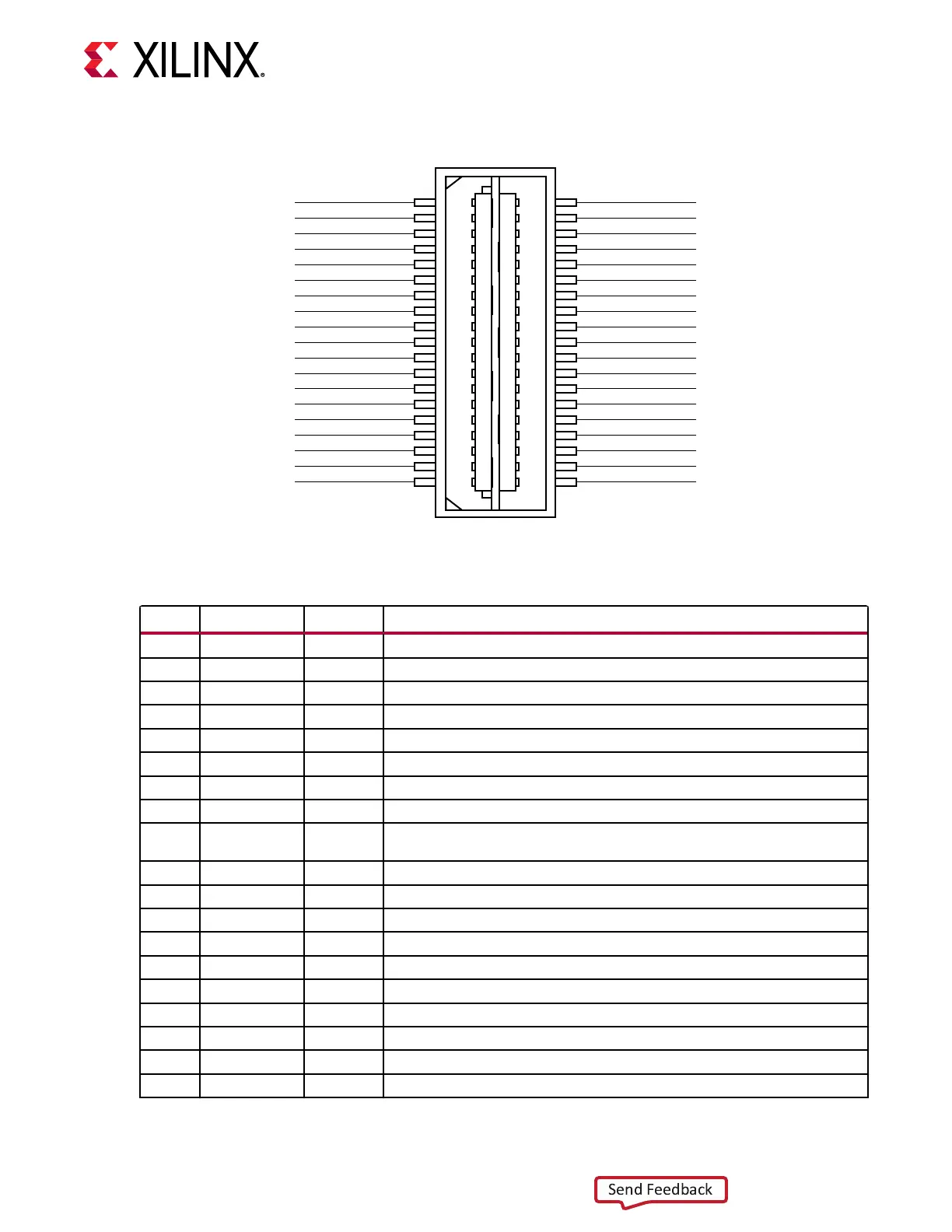

Figure 17: MICTOR Connector Pinout

NC 3

NC 1

GND 5

SRST_B 9

DBGRQ 7

TDO 11

TCK 15

RTCK 13

TMS 17

TRST_B 21

TDI 19

TRACEDATA[15] 23

TRACEDATA[13] 27

TRACEDATA[14] 25

TRACEDATA[12] 29

TRACEDATA[10] 33

TRACEDATA[11] 31

TRACEDATA[9] 35

TRACEDATA[8] 37

4

2

6

10

8

12

16

14

18

22

20

24

28

26

30

34

32

36

38

NC

NC

TRACE CLK

EXTTRIG

DBGACK

VTREF

TRACEDATA[7]

NC

TRACEDATA[6]

TRACEDATA[4]

TRACEDATA[5]

TRACEDATA[3]

TRACEDATA[1]

TRACEDATA[2]

Logic 0

Logic 1

Logic 0

TRACECTL

TRACEDATA[0]

X25134-022321

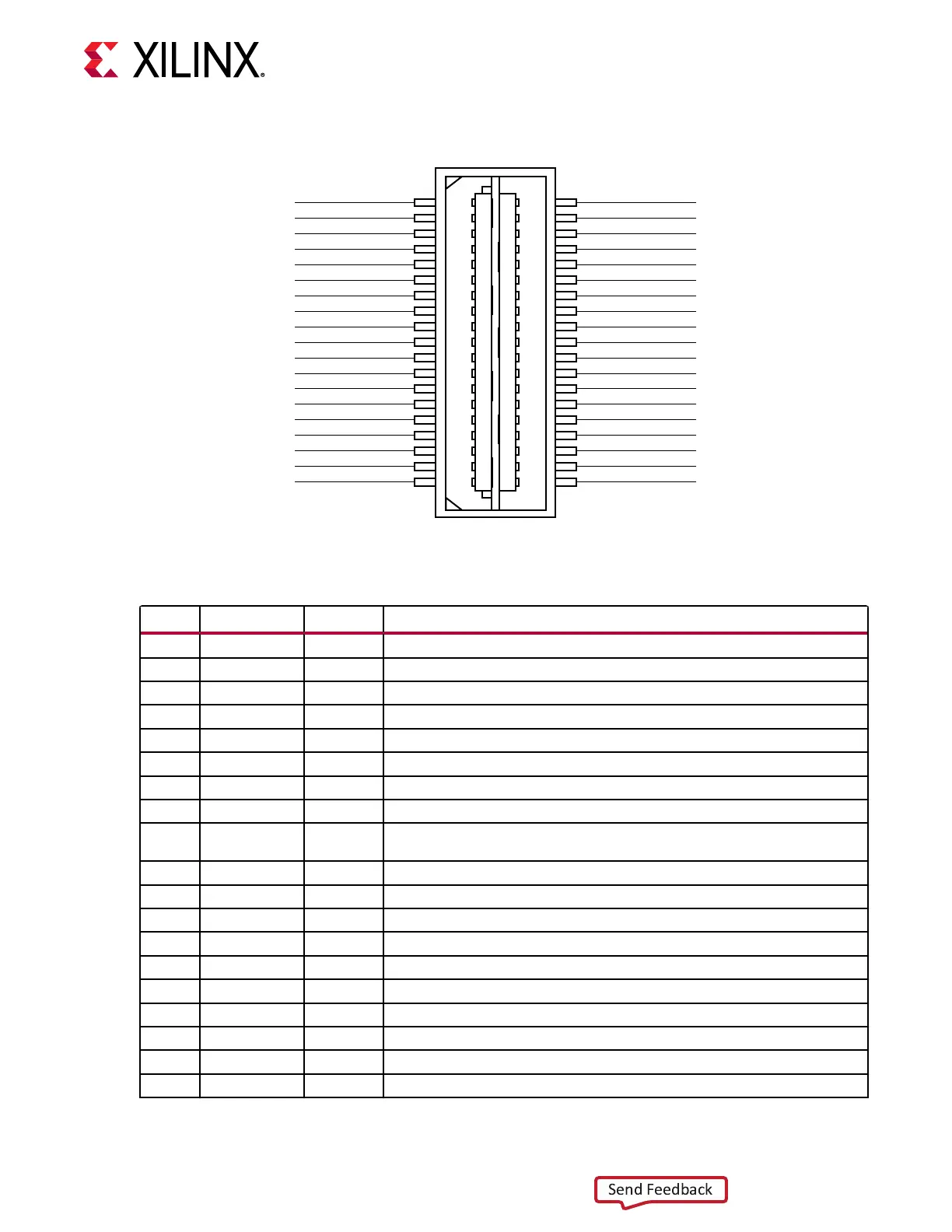

Table 10: Signal Descriptions

Pin Name Direction Description

1, 2, 3, 4 - - No connection

5 GND Power Ground return

6 TRACE_CLK Input Trace clock

7 DBGRQ Output Debug request. Pulled to GND through 4.7 KΩ resistor

8 DBGACK Input Debug acknowledge. Pulled to GND through 4.7 KΩ resistor

9 SRST_B Output System reset. Pulled up to VTREF through 4.7 KΩ resistor

10 EXTTRIG Input External trigger

11 TDO Input JTAG Test Data Out. Pulled up to VTREF through 4.7 KΩ resistor

12 VTREF Input Voltage target reference. Used to set the interface I/O levels. Supports voltages

in the range of 1.2V to 3.6V.

13 RTCK Input Return test clock. Pulled up to VTREF through 4.7 KΩ resistor

14 - - No connection

15 TCK Output JTAG Test Clock. Pulled up to VTREF through 4.7 KΩ resistor

16 TRACEDATA7 Input Trace data 7

17 TMS Output JTAG Test Mode Select. Pulled up to VTREF through 4.7 KΩ resistor

18 TRACEDATA6 Input Trace data 6

19 TDI Output JTAG Test Data In. Pulled up to VTREF through 4.7 KΩ resistor

20 TRACEDATA5 Input Trace data 5

21 TRST_B Output JTAG Test Reset. Pulled up to VTREF through 4.7 KΩ resistor

22 TRACEDATA4 Input Trace data 4

Chapter 10: Parallel Debug Interface

UG1514 (v1.0) March 8, 2021 www.xilinx.com

SmartLynq Module+ 36

Loading...

Loading...