Copyright © 2015 Avnet, Inc. AVNET and the AV logo are registered trademarks of Avnet, Inc. All other brands are property of their respective owners.

Avnet Electronics Marketing 13 of 28 Rev D 24 Apr 2015

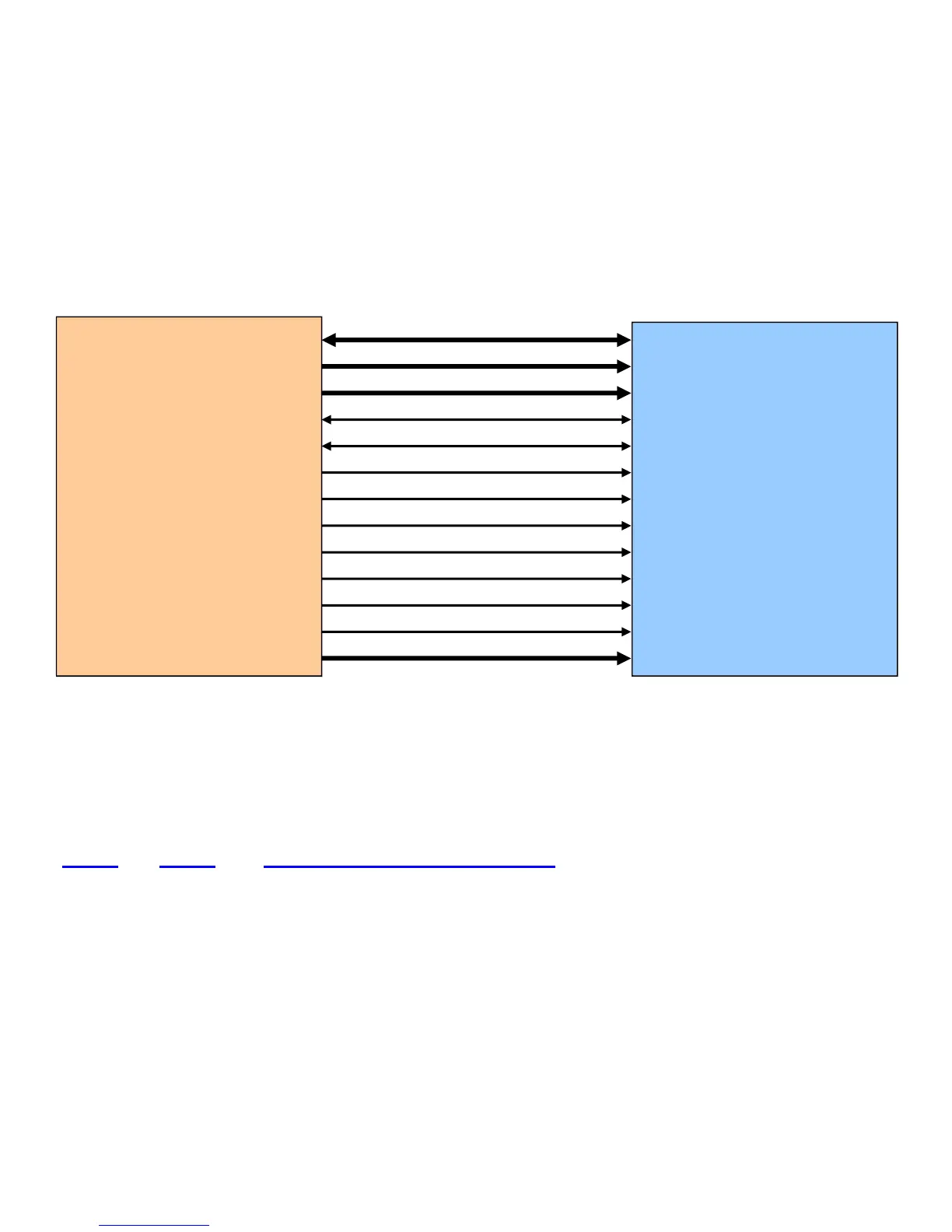

2.3.1 32 Mb x 16 (64MB) Micron LPDDR Mobile SDRAM component

The Micron LPDDR mobile SDRAM device, part number MT46H32M16LFBF-5, provides a double data rate

architecture to achieve high-speed operation. The device provides 64 MB and it is internally configured as a

quad-bank DRAM of memory on a single IC. Each of the x16’s 134,217,728-bit banks is organized as 8,192

rows by 1,024 columns by 16 bits. The device has an operating voltage of 1.8V and the interface is

MOBILE_DDR. The Spartan-6 Memory Controller Block supports up to 400 Mb/s (200 MHz double data rate)

performance. The following figure shows a high-level block diagram of the LPDDR Mobile SDRAM interface

on the MicroBoard:

Figure 6 – Spartan-6 FPGA LX9 LPDDR Mobile SDRAM Interface

The LPDDR signals are connected to I/O Bank 3 of the Spartan-6 FPGA LX9 FPGA. The voltage supply pins

(VCCO) for the LPDDR bank are connected to the 1.8V supply rail. This supply rail can be measured across

the 100uF Capacitor C22.

It is highly recommended that anyone creating a Spartan-6 MCB design thoroughly read the two User Guides

(UG388 and UG416), the MIG Master Answer Record 33566, and the associated Answer Records linked

from that Master Record.

The following table provides timing and other information about the Micron device necessary to implement a

DDR2 memory controller.

S6LX9

CSG324

Bank 3

12:0

BA[1:0]

LD

S

UD

S

LDM

UDM

CAS

RAS

WE#

CS#

CKE

CK_P/N

LPDDR

Mobile SDRAM

DQ[15:0]

Loading...

Loading...