Copyright © 2015 Avnet, Inc. AVNET and the AV logo are registered trademarks of Avnet, Inc. All other brands are property of their respective owners.

Avnet Electronics Marketing 18 of 28 Rev D 24 Apr 2015

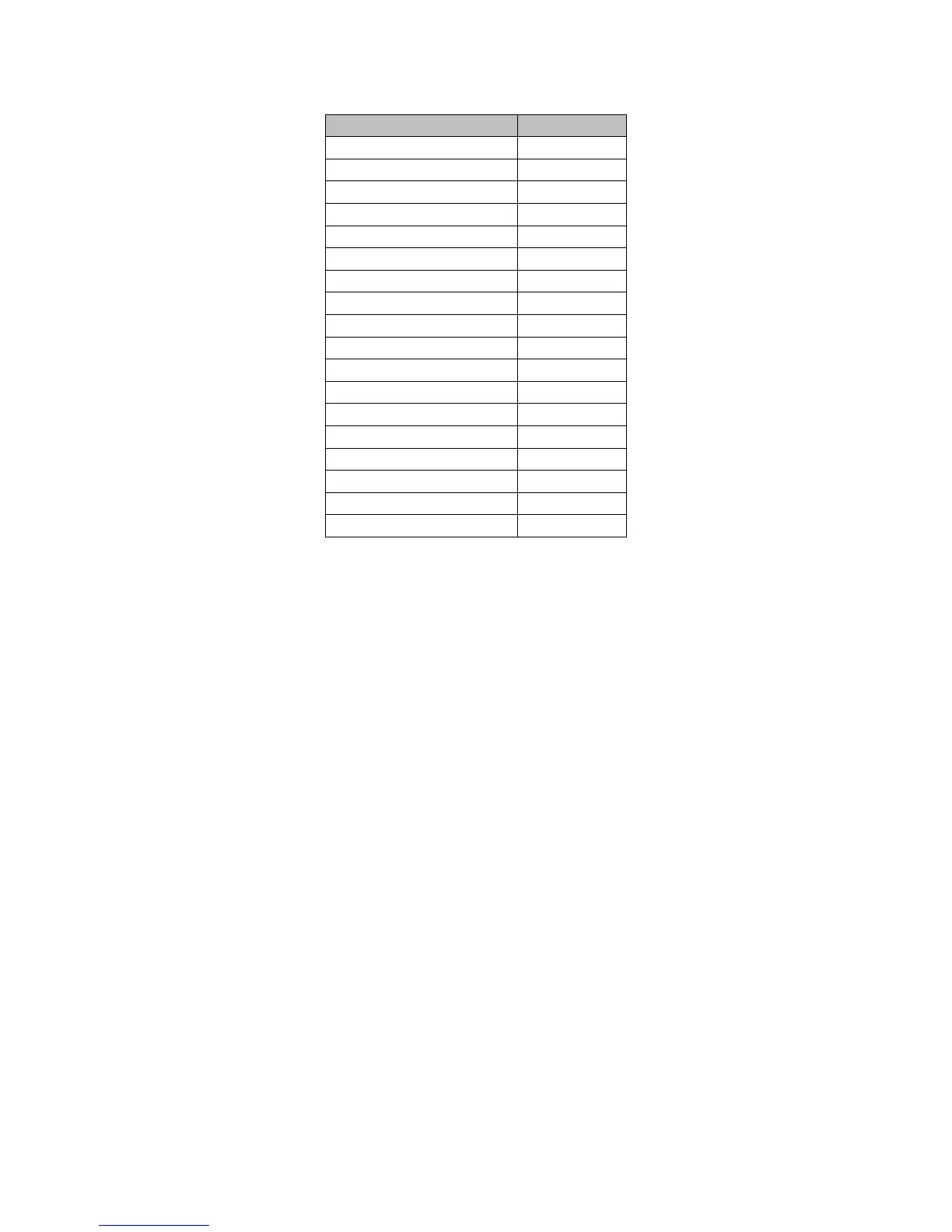

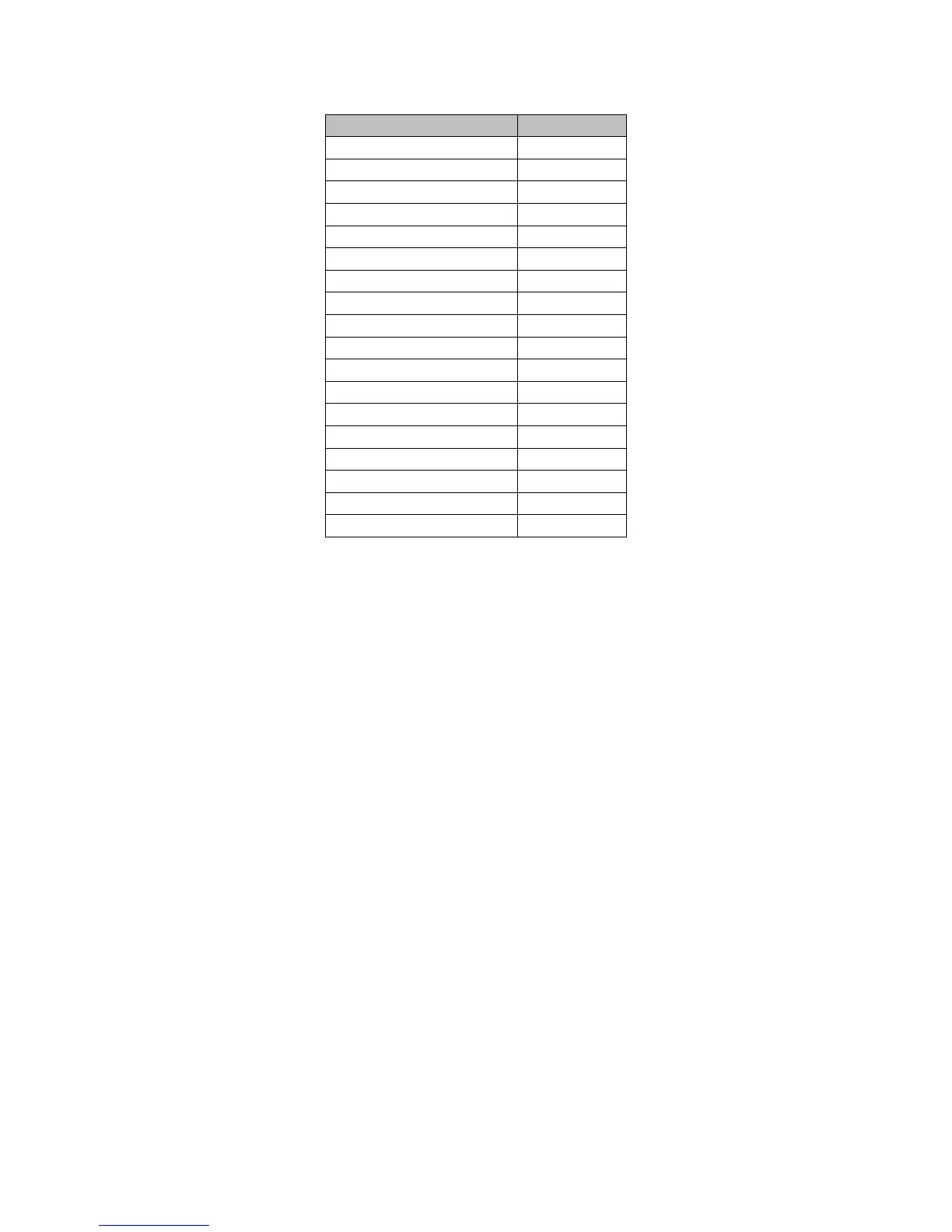

Table 9 – 10/100 Pin Assignments

Net Name FPGA Pin#

FPGA_ETH_MDC M16

FPGA_ETH_MDIO L18

FPGA_ETH_RX_CLK L15

FPGA_ETH_RX_D0 T17

FPGA_ETH_RX_D1 N16

FPGA_ETH_RX_D2 N15

FPGA_ETH_RX_D3 P18

FPGA_ETH_RX_ER N18

FPGA_ETH_DV P17

FPGA_ETH_TX_CLK H17

FPGA_ETH_TX_D0 K18

FPGA_ETH_TX_D1 K17

FPGA_ETH_TX_D2 J18

FPGA_ETH_TX_D3 J16

FPGA_ETH_TX_EN L17

FPGA_ETH_COL M18

FPGA_ETH_CRS N17

FPGA_ETH_RESET# T18

Please note that the PHY Address pins are not strapped on the board. The Avnet XBD for this board places

pull-ups on the AD[4:1] pins. The AD[0] pin is shared with COL, which gets stripped out of EDK 12.4

xps_ethernetlite full duplex designs. The default bitgen options result in this now unused pin getting pulled-

low, which results in a PHY Address of 11110b. If the bitgen options are changed such that UnusedPins are

PullNone, then the PHY Address will be 11111b due to the internal PHY pull-up on AD[0]. The user must be

aware that not controlling these PHY AD pins with internal pull-up and bitgen options will result in a PHY

Address of 00000b, which puts the PHY into Isolate Mode, and it will not operate correctly.

Loading...

Loading...