VC7222 IBERT Getting Started Guide www.xilinx.com 31

UG971 (v5.0) June 12, 2014

Running the GTZ IBERT Demonstration

Setting up the Vivado Design Suite Software

The procedure to launch the Vivado Suite is detailed in Setting Up the Vivado Design Suite

Software, page 15.

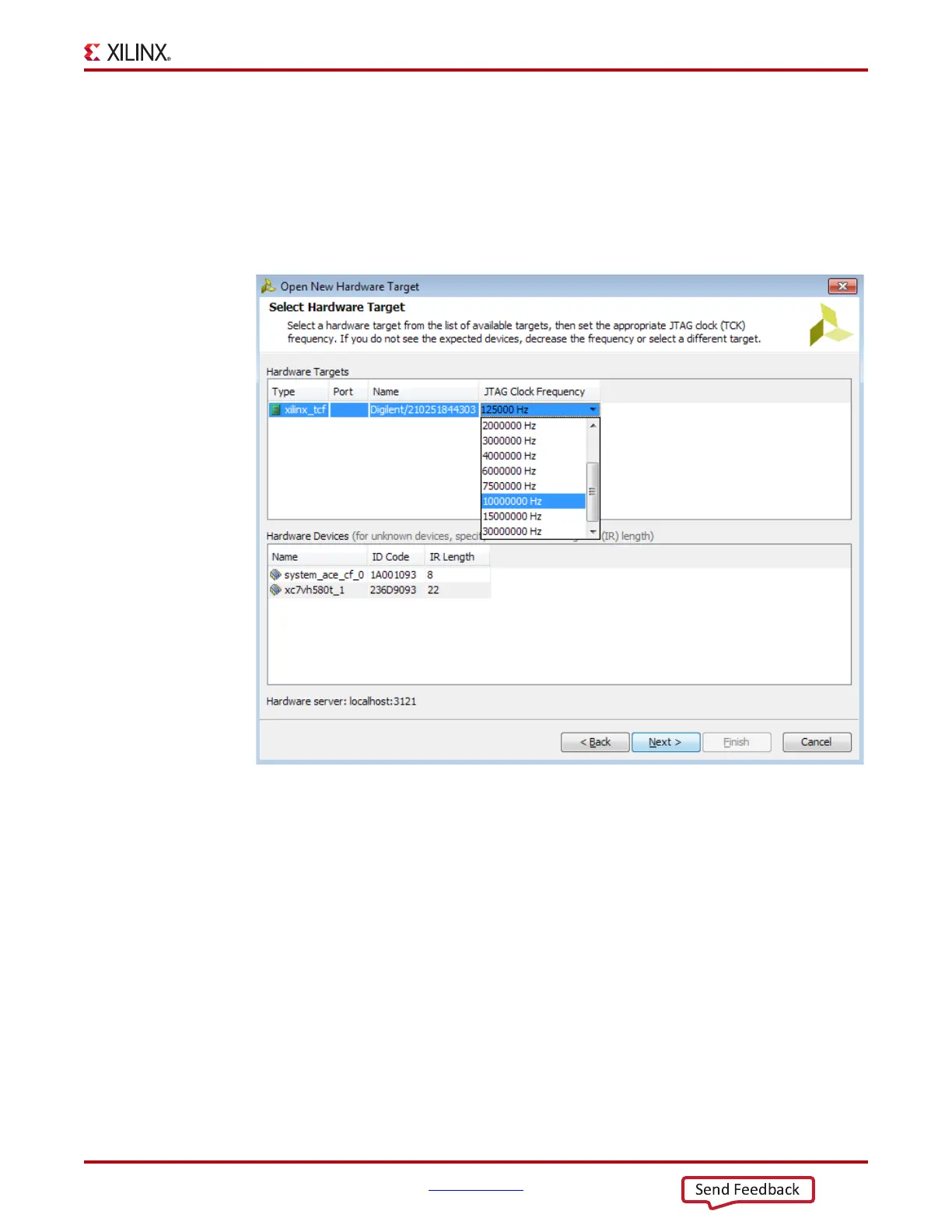

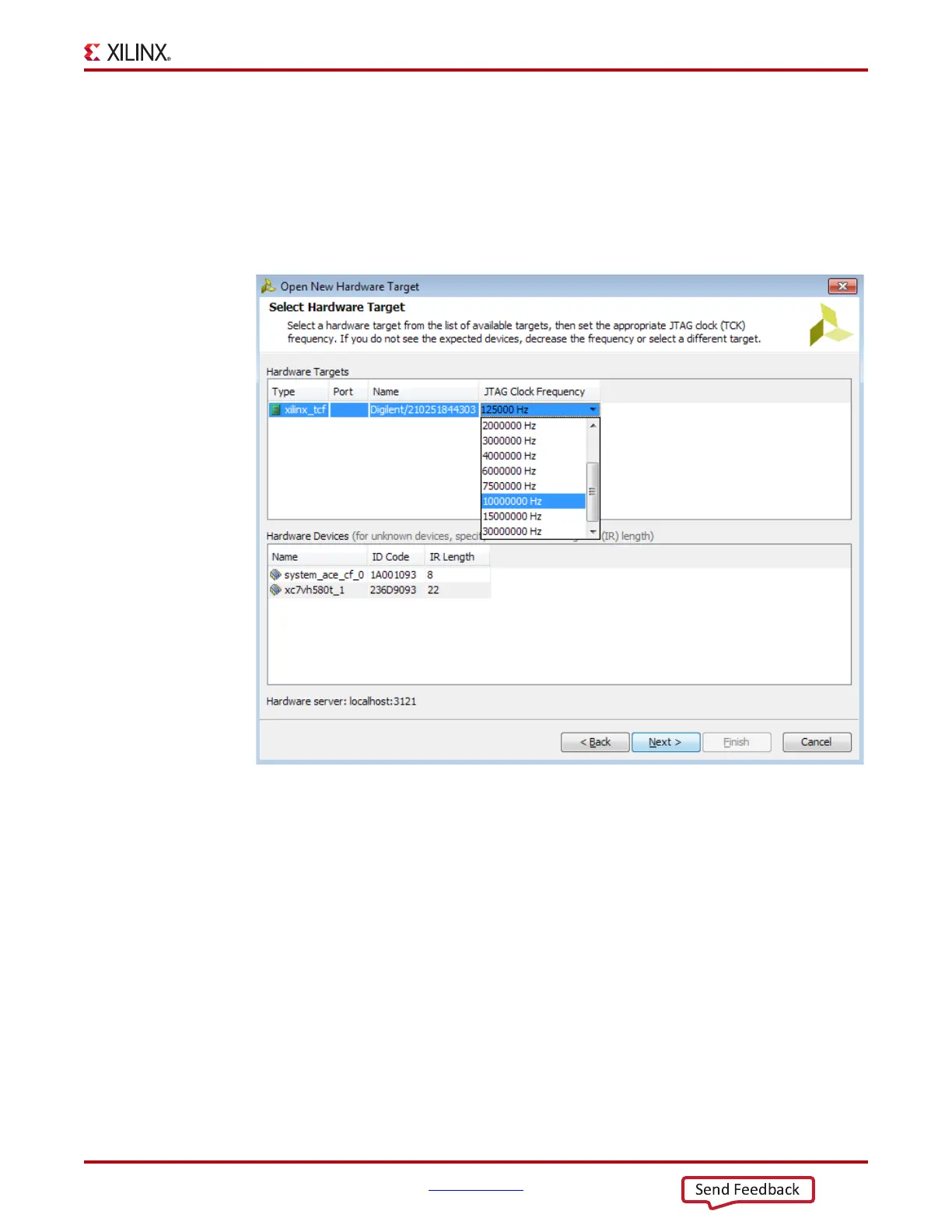

In the Open Hardware Target window it is highly recommended to lower the JTAG clock

frequency to 10 MHz or lower for reliable JTAG communication during the GTZ demo

(Figure 1-26).

Starting the SuperClock-2 Module

The IBERT demonstration designs use an integrated VIO core to control the clocks on the

SuperClock-2 module. The SuperClock-2 module features two clock-source components:

• An always-on Si570 crystal oscillator

• An Si5368 jitter-attenuating clock multiplier

Outputs from either source can be used to drive the transceiver reference clocks.

X-Ref Target - Figure 1-26

Figure 1-26: Select Hardware Target

Loading...

Loading...