September 18, 1996 (Version 1.04) 4-21

Fast Carry Logic

Each CLB F and G function generator contains dedicated

arithmetic logic for the fast generation of carry and borrow

signals. This extra output is passed on to the function gen-

erator in the adjacent CLB. The carry chain is independent

of normal routing resources.

Dedicated fast carry logic greatly increases the efficiency

and performance of adders, subtractors, accumulators,

comparators and counters. It also opens the door to many

new applications involving arithmetic operation, where the

previous generations of FPGAs were not fast enough or too

inefficient. High-speed address offset calculations in

microprocessor or graphics systems, and high-speed addi-

tion in digital signal processing are two typical applications.

The two 4-input function generators can be configured as a

2-bit adder with built-in hidden carry that can be expanded

to any length. This dedicated carry circuitry is so fast and

efficient that conventional speed-up methods like carry

generate/propagate are meaningless even at the 16-bit

level, and of marginal benefit at the 32-bit level.

This fast carry logic is one of the more significant features

of the XC4000 Series, speeding up arithmetic and counting

into the 70 MHz range.

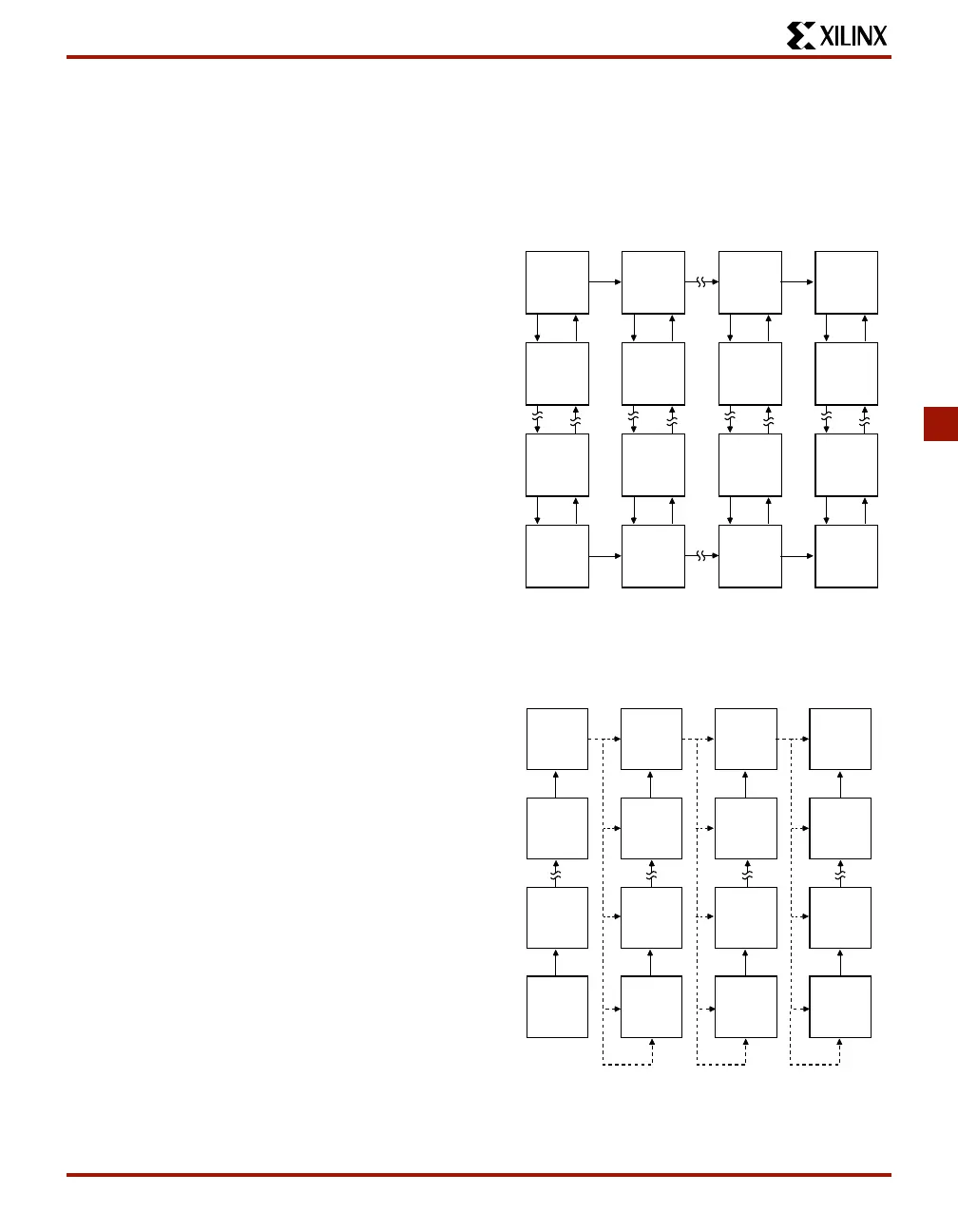

The carry chain in XC4000E devices can run either up or

down. At the top and bottom of the columns where there

are no CLBs above and below, the carry is propagated to

the right. (See Figure 11.) In order to improve speed in the

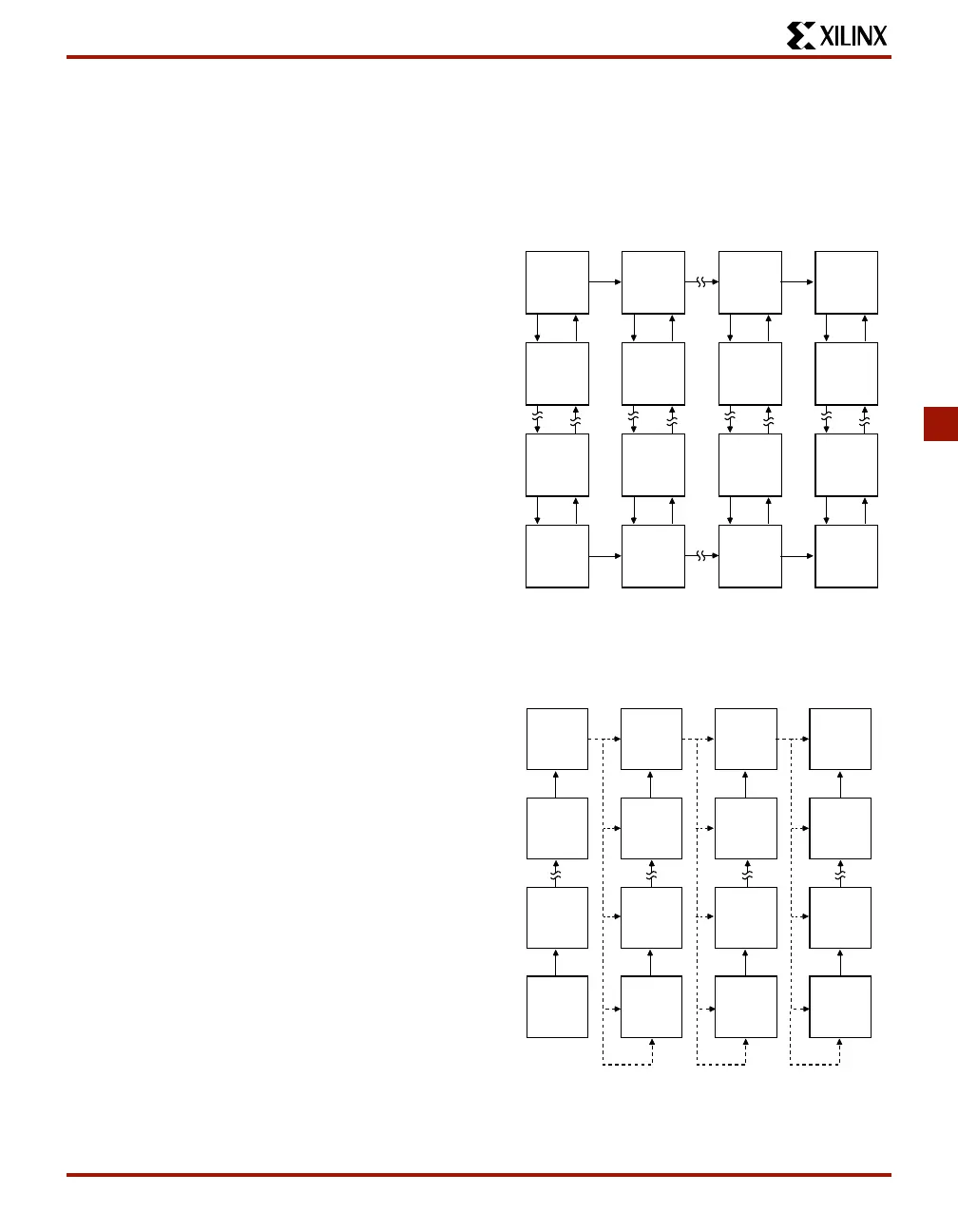

high-capacity XC4000EX devices, which can potentially

have very long carry chains, the carry chain travels upward

only, as shown in Figure 12. This restriction should have lit-

tle impact, because the smallest XC4000EX device, the

XC4028EX, can accommodate a 64-bit carry chain in a sin-

gle column. Additionally, standard interconnect can be

used to route a carry signal in the downward direction.

Figure 13 on page 22 shows an XC4000E CLB with dedi-

cated fast carry logic. The carry logic in the XC4000EX is

similar, except that COUT exits at the top only, and the sig-

nal CINDOWN does not exist. As shown in Figure 13, the

carry logic shares operand and control inputs with the func-

tion generators. The carry outputs connect to the function

generators, where they are combined with the operands to

form the sums.

Figure 14 and Figure 15 on page 23 show the details of the

carry logic for the XC4000E and the XC4000EX respec-

tively. These diagrams show the contents of the box

labeled “CARRY LOGIC” in Figure 13. As shown, the

XC4000EX carry logic eliminated a multiplexer to reduce

delay on the pass-through carry chain. Additionally, the

multiplexer on the G4 path now has a memory-programma-

ble input, which permits G4 to directly connect to COUT.

G4 thus becomes an additional high-speed initialization

path for carry-in.

The dedicated carry logic is discussed in detail in Xilinx

document XAPP 013: “

Using the Dedicated Carry Logic in

XC4000

.” This discussion also applies to XC4000E

devices, and to XC4000EX devices when the minor logic

changes are taken into account.

The fast carry logic can be accessed by placing special

library symbols, or by using Xilinx Relationally Placed Mac-

ros (RPMs) that already include these symbols.

X6687

CLB CLB CLB CLB

CLB CLB CLB CLB

CLB

CLB

CLB

CLB

CLB

CLB

CLB

CLB

Figure 11: Available XC4000E Carry Propagation

Paths

X6610

CLB CLB CLB CLB

CLB CLB CLB CLB

CLB

CLB

CLB

CLB

CLB

CLB

CLB

CLB

Figure 12: Available XC4000EX Carry Propagation

Paths (dotted lines use general interconnect)

Loading...

Loading...