140 IBM eX5 Implementation Guide

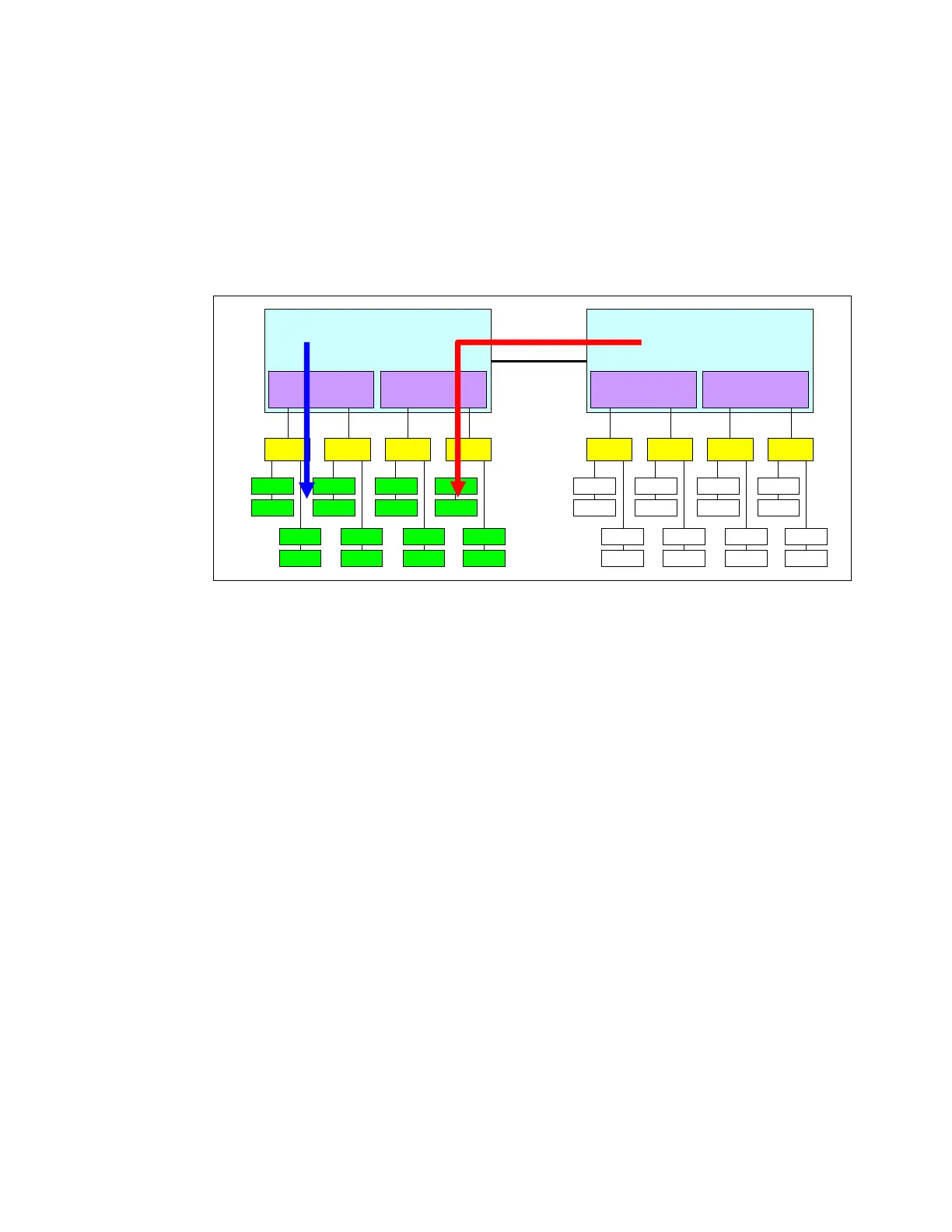

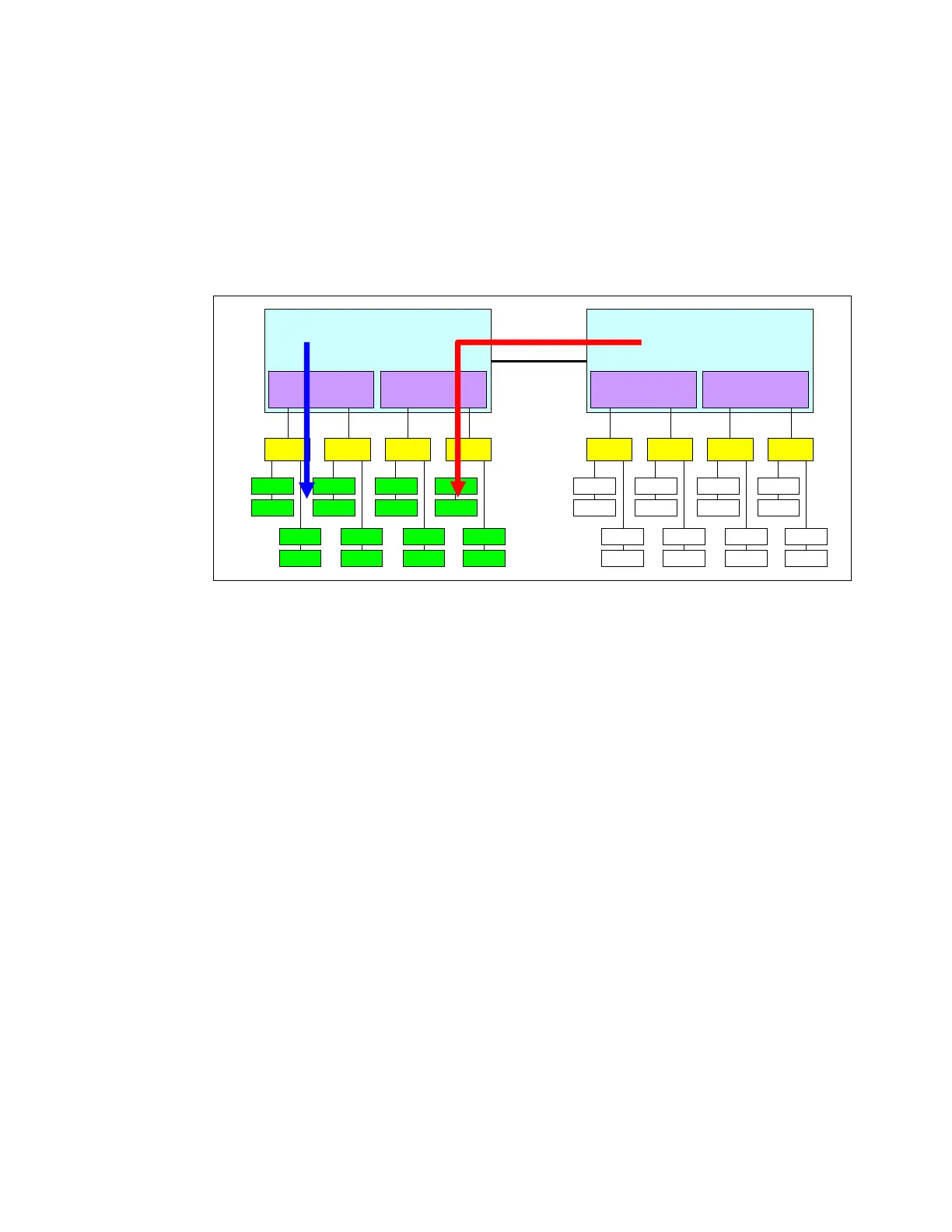

access only to remote or “far” memory. So, threads executing on Processor 1 have a longer

latency to access memory as compared to threads on Processor 0. This situation is due to

the latency penalty incurred to traverse the QPI links to access the data on the other

processor’s memory controller. The bandwidth to remote memory is also limited by the

capability of the QPI links. The latency to access remote memory is more than 50% higher

than local memory access.

For these reasons, we advise that you populate all processors with memory, remembering the

requirements that are necessary to ensure optimal interleaving and Hemisphere Mode.

Figure 4-17 Memory latency when not spreading DIMMs across both processors

4.8.5 Mixing DIMMs and the performance effect

Using DIMMs of various capacities is supported for several reasons:

Not all applications require the full memory capacity that a homogenous memory

population provides.

Cost-saving requirements might dictate using a lower memory capacity for part of the

platform’s DIMMs.

Figure 4-18 on page 141 illustrates the relative performance of three mixed memory

configurations as compared to a baseline of a fully populated memory configuration. While

these configurations use 4 GB (4R x8) and 2 GB (2R x8) DIMMs as specified, similar trends

to this data are expected when using other mixed DIMM capacities. In all cases, memory is

populated in minimum groups of four, as specified in the following configurations, to ensure

that Hemisphere Mode is maintained.

Figure 4-18 on page 141 shows the following configurations:

Configuration A: Full population of equivalent capacity DIMMs (2 GB). This configuration

represents an optimally balanced configuration.

Configuration B: Each memory channel is balanced with the same memory capacity, but

half of the DIMMs are of one capacity (4 GB) and half are of another capacity (2 GB).

Configuration C: Eight DIMMs of one capacity (4 GB) are populated across the eight

memory channels, and four additional DIMMs of another capacity (2 GB) are installed one

per memory buffer, so that Hemisphere Mode is maintained.

Configuration D: Four DIMMs of one capacity (4 GB) are populated across four memory

channels, and four DIMMs of another capacity (2 GB) are populated on the other four

QPI links

Intel Xeon 7500

Processor 0

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMMDIMM

Buffer Buffer Buffer Buffer

Memory

controller

Memory

controller

Intel Xeon 7500

Processor 1

DIMM

DIMM

DIMMDIMM

Buffer Buffer Buffer Buffer

Memory

controller

Memory

controller

LOCAL

REMOTE

Loading...

Loading...