7-10

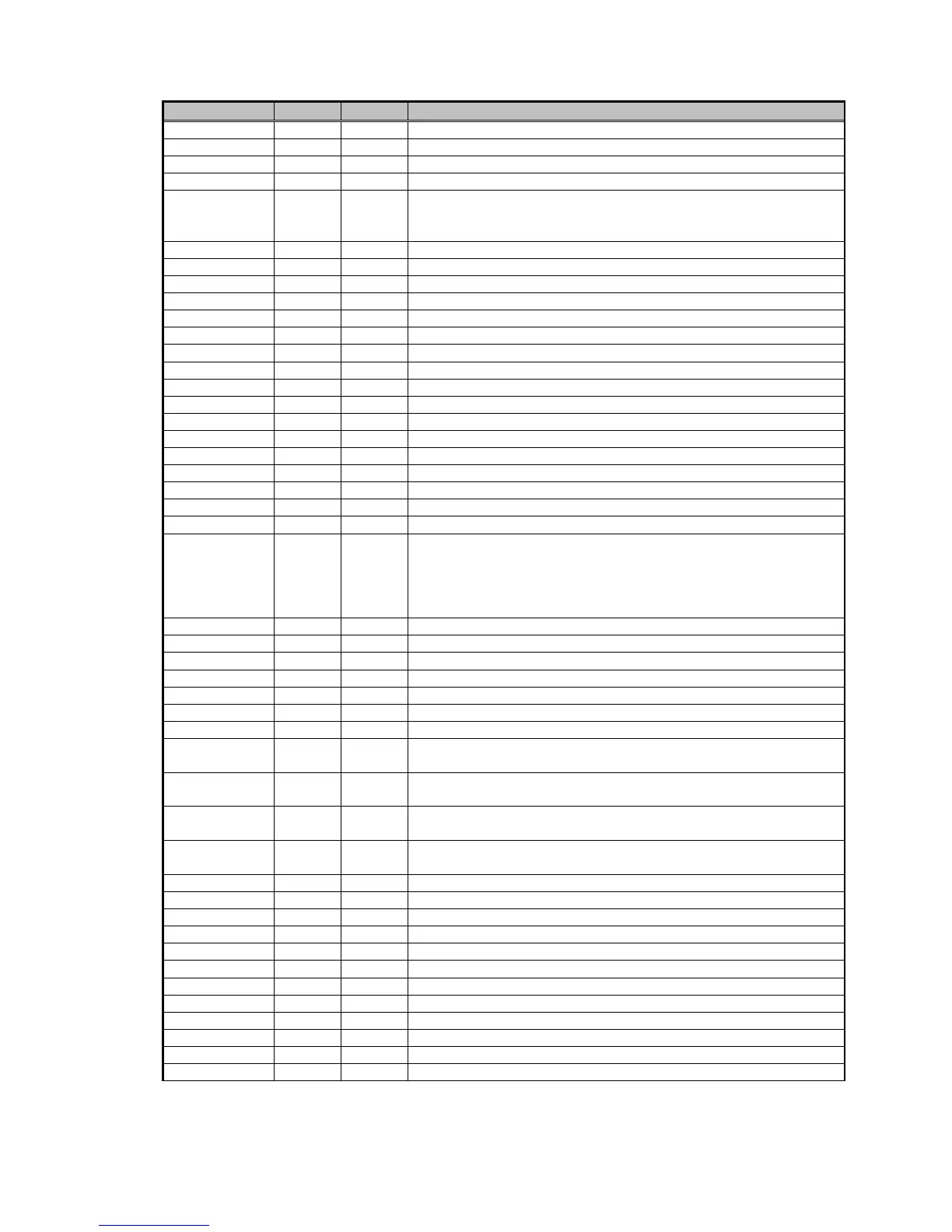

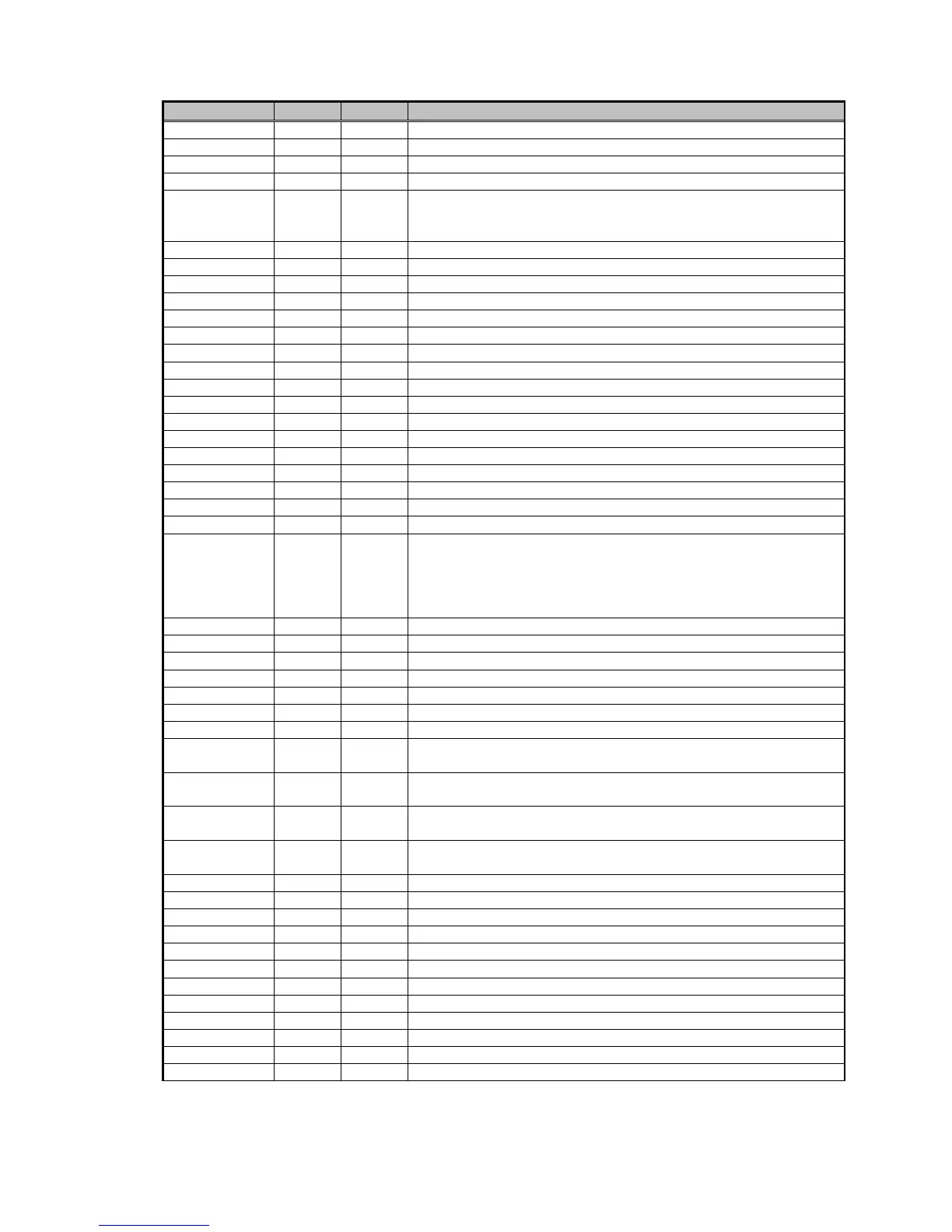

2.4.4 Pin description

Symbol Pin # I/O Description

B_IN10

1 I Channel B Data Input Color Blue (LSB)

B_IN11

2 I Channel B Data Input Color Blue

B_IN12

3 I Channel B Data Input Color Blue

B_IN13

4 I Channel B Data Input Color Blue

DATA_SEL

5 I Indicate Channel A or Channel B contains valid input data:

1: data in Channel A is valid

0: data in Channel B is valid

B_IN14

6 I Channel B Data Input Color Blue

B_IN15

7 I Channel B Data Input Color Blue

B_IN16

8 I Channel B Data Input Color Blue

B_IN17

9 I Channel B Data Input Color Blue (MSB)

ROM_SCL

10 O SCL in I

2

C for EEPROM interface

ROM_SDA

11 I/O SDA in I

2

C for EEPROM interface

GND

12 Ground

CPU_SCL

13 I SCL in I

2

C for CPU interface

CPU_SDA

14 I/O SDA in I

2

C for CPU interface

PWM_CTL

15 O PWM control signal (Detail description in PWM Operation Section)

CLK_1M

16 I Free Running Clock (default: 1MHz)

VDD

17 Power Supply

CLK_1M_O

18 O Feedback of free Running Clock

RESET_B

19 I System Reset (active LOW)

R_OSM

20 I OSM Color Red

G_OSM

21 I OSM Color Green

B_OSM

22 I OSM Color Blue

EN_OSM

23 I OSM Mixer Enable

=0, No OSM output

=1, R_OUT[7:0] = {R_OSM repeat 8 times}

G_OUT[7:0] = {G_OSM repeat 8 times}

B_OUT[7:0] = {B_OSM repeat 8 times}

SCAN_EN

24 I Manufacturing test pin (NC)

TEST_EN

25 I Manufacturing test pin (NC)

VCLK01

26 I Input Clock 1

FCLK0

27 O Input PLL Feedback Clock

VCLK00

28 I Input Clock 0

FCLK1

29 O Output PLL Feedback Clock

VCLK1

30 I Output PLL Output Clock

HSYNC_O

31 O Output HSYNC (the polarity is programmable through CPU,

default is active low)

VSYNC_O

32 O Output VSYNC (the polarity is programmable through CPU,

default is active low)

DCLK_OUT

33 O Output Clock to Control Panel (the polarity is Programmable

through CPU)

DE_OUT

34 O Output Display Enable for Panel (the polarity is Programmable

through CPU, default is active HIGH)

GND

35 Ground

VDD

36 Power Supply

R_OUT0_E

37 O Output Color Red Even Pixel (left pixel)

R_OUT1_E

38 O Output Color Red Even Pixel (left pixel)

R_OUT2_E

39 O Output Color Red Even Pixel (left pixel)

R_OUT3_E

40 O Output Color Red Even Pixel (left pixel)

VDD

46 Power Supply

R_OUT5_E

47 O Output Color Red Even Pixel (left pixel)

GND

48 Ground

R_OUT6_E

49 O Output Color Red Even Pixel (left pixel)

R_OUT7_E

50 O Output Color Red Even Pixel (left pixel)

GND

51 Ground

Loading...

Loading...