7-14

2.6 CPU (MTV112MN32) description

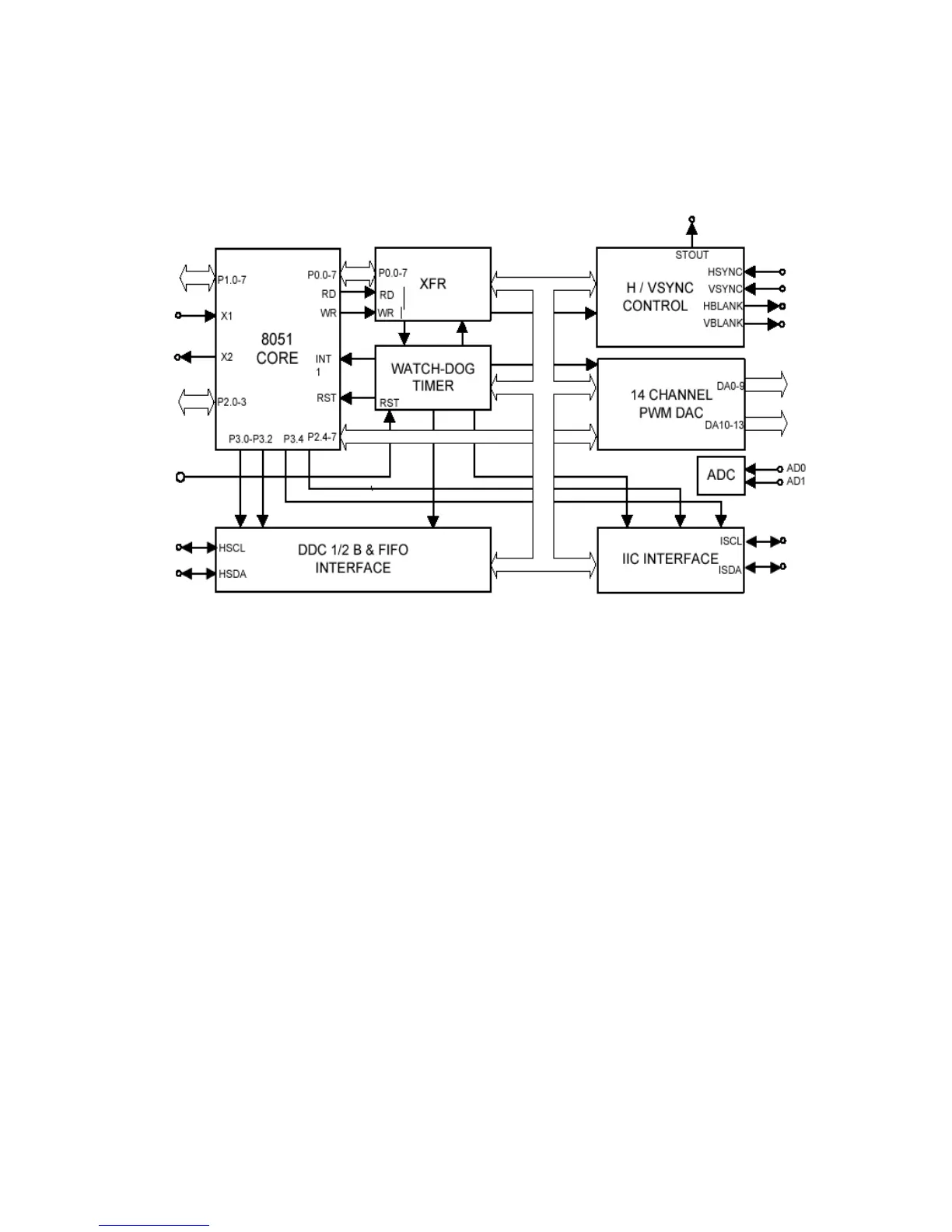

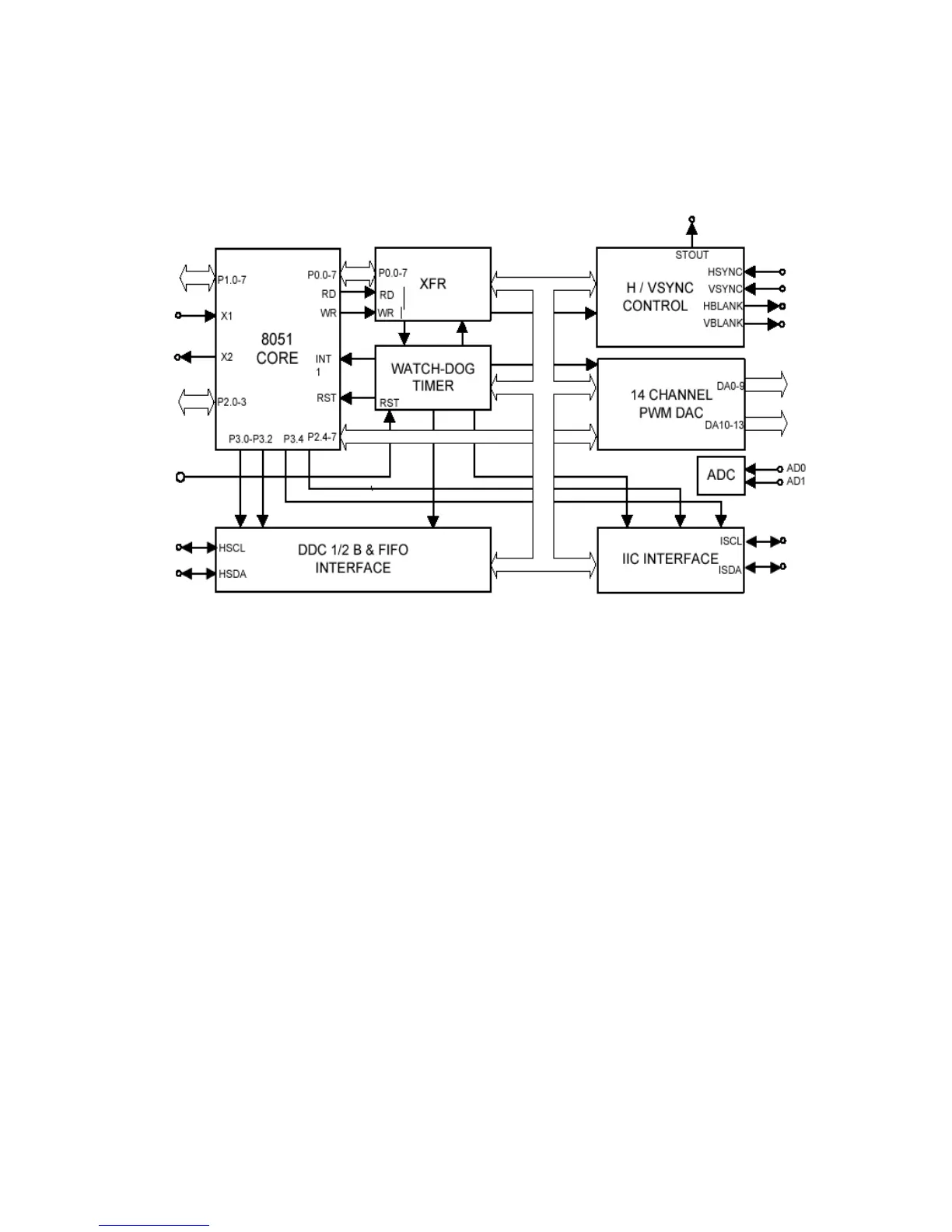

2.6.1 CPU internal block

The MTV112MN32 micro-controller is an 8051 CPU core embedded device specially tailored to LCD monitor

applications. It includes an 8051 CPU core, 256 bytes SRAM, fourteen built-in PWMDACs, DDC1/DDC2B

interface, 24Cxx series EEPROM interface, A/D converter and a 32K bytes internal program EPROM.

2.6.2 Features

8051 core.

384 bytes internal RAM.

32K bytes program EPROM

14 channels 10V open drain PWM DAC, 10 dedicated channels and 4 channels shared with I/O pin.

20 bi-direction I/O pin, 12 dedicated pin, 4 shared with DAC, 4 shared with DDC/IIC interface.

3-output pin shared with H/V sync output and self test output pins.

SYNC processor for composite separation, polarity and frequency check, and polarity adjust.

Built-in monitor self-test pattern generator.

Built-in Low Power Reset circuit.

One slave mode IIC interface and one master mode IIC interface.

IIC interface for DDC1/DDC2B and EEPROM, only one EEPROM needed to store DDC1/DDC2B and

display mode information.

Dual 4 bit ADC.

Watch dog timer with programmable interval.

Loading...

Loading...