7-27

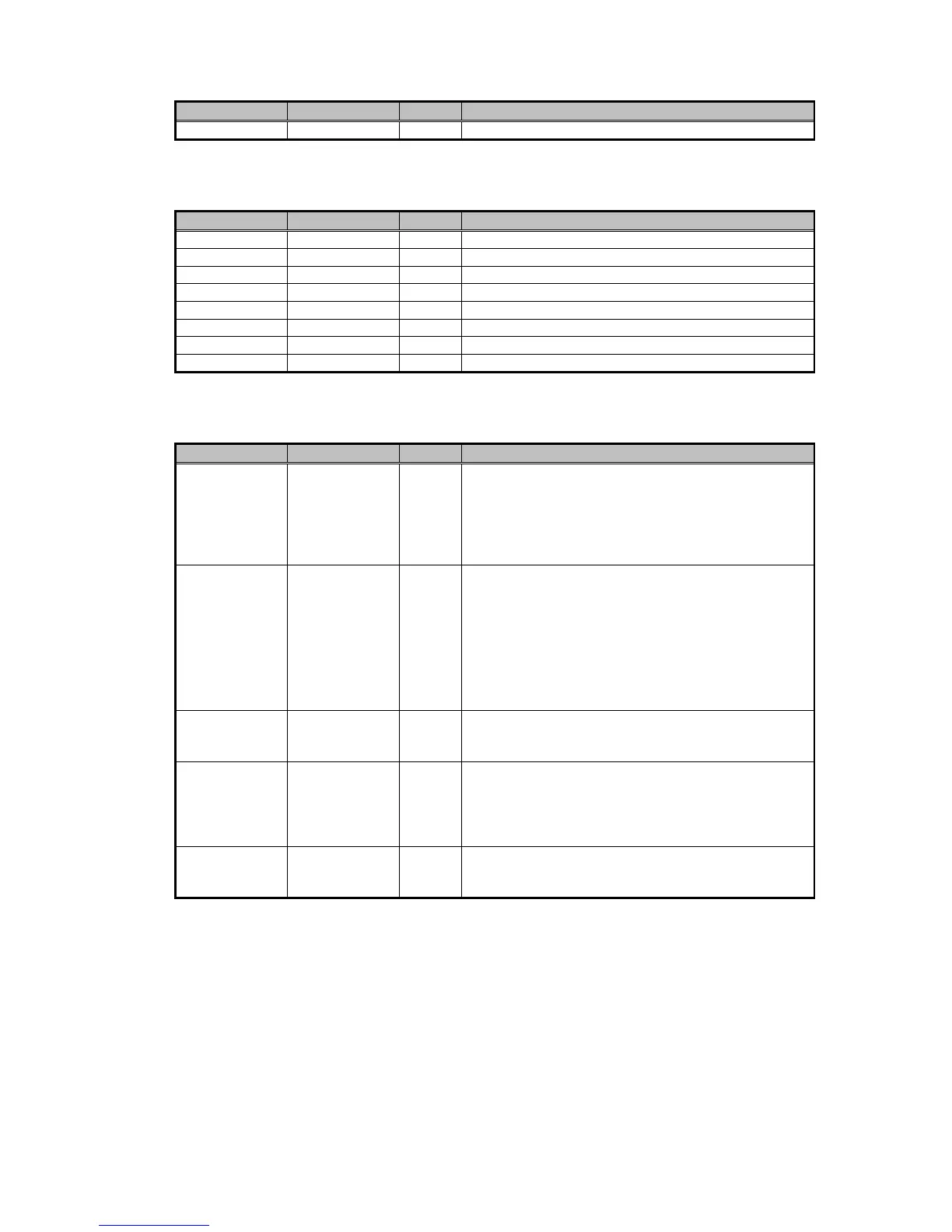

Reserved Pin Description

Pin Name Pin # Type Description

Reserved

99 In Must be tied HIGH for normal operation.

Power and Ground Pin Description

Pin Name Pin # Type Description

VCC

6,38,67 Power Digital Core VCC, must be set to 3.3V.

GND

5,39,68 Ground Digital Core GND.

OVCC

18,29,43,57,78 Power Output VCC, must be set to 3.3V.

OGND

19,28,45,58,76 Ground Output GND.

AVCC

82,84,88,95 Power Analog VCC must be set to 3.3V.

AGND

79,83,87,89,92 Ground Analog GND.

PVCC

97 Power PLL Analog VCC must be set to 3.3V.

PGND

98 Ground PLL Analog GND.

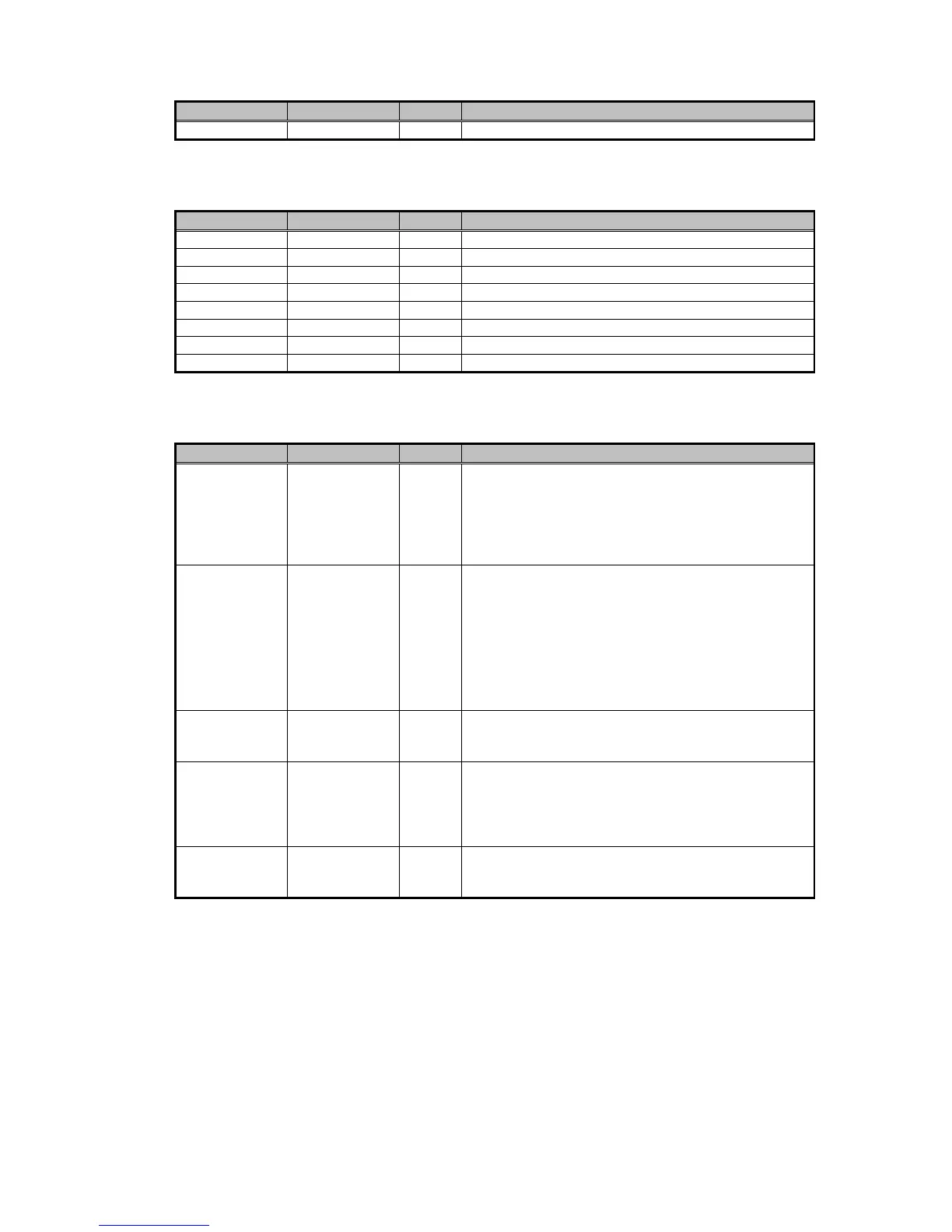

Configuration Pins Description

Pin Name Pin # Type Description

OCK_INV

100 In ODCK Polarity.

A LOW level selects normal ODCK output. A HIGH

level selects inverted ODCK output. All other output

signals are not affected by this pin. They will

maintain the same timing no matter the setting of

OCK_INV pin.

PIXS

4 In Pixel Select.

A LOW level indicates one pixel (up to 24-bits) per

clock mode using

QE[23:0] A HIGH level indicates two pixels (up to

48-bits) per clock mode using

QE[23:0] for first pixel and QO[23:0] for second

pixel.

DFO

1 In Output Data Format.

For all DVI applications, this pin should be tied

LOW.

STAG_OUT

7 In Staggered Output.

A HIGH level selects normal simultaneous outputs

on all odd and even data lines. A LOW level selects

staggered output drive. This function is only

available in 2-pixels per clock mode.

ST

3 In Output Drive.

A HIGH level selects HIGH output drive strength. A

LOW level selects LOW output drive strength.

Loading...

Loading...