LTE Standard Module Series

Clock and mode can be configured by AT command, and the default configuration is short frame

synchronization format with 2048 kHz PCM_CLK and 8 kHz PCM_SYNC.

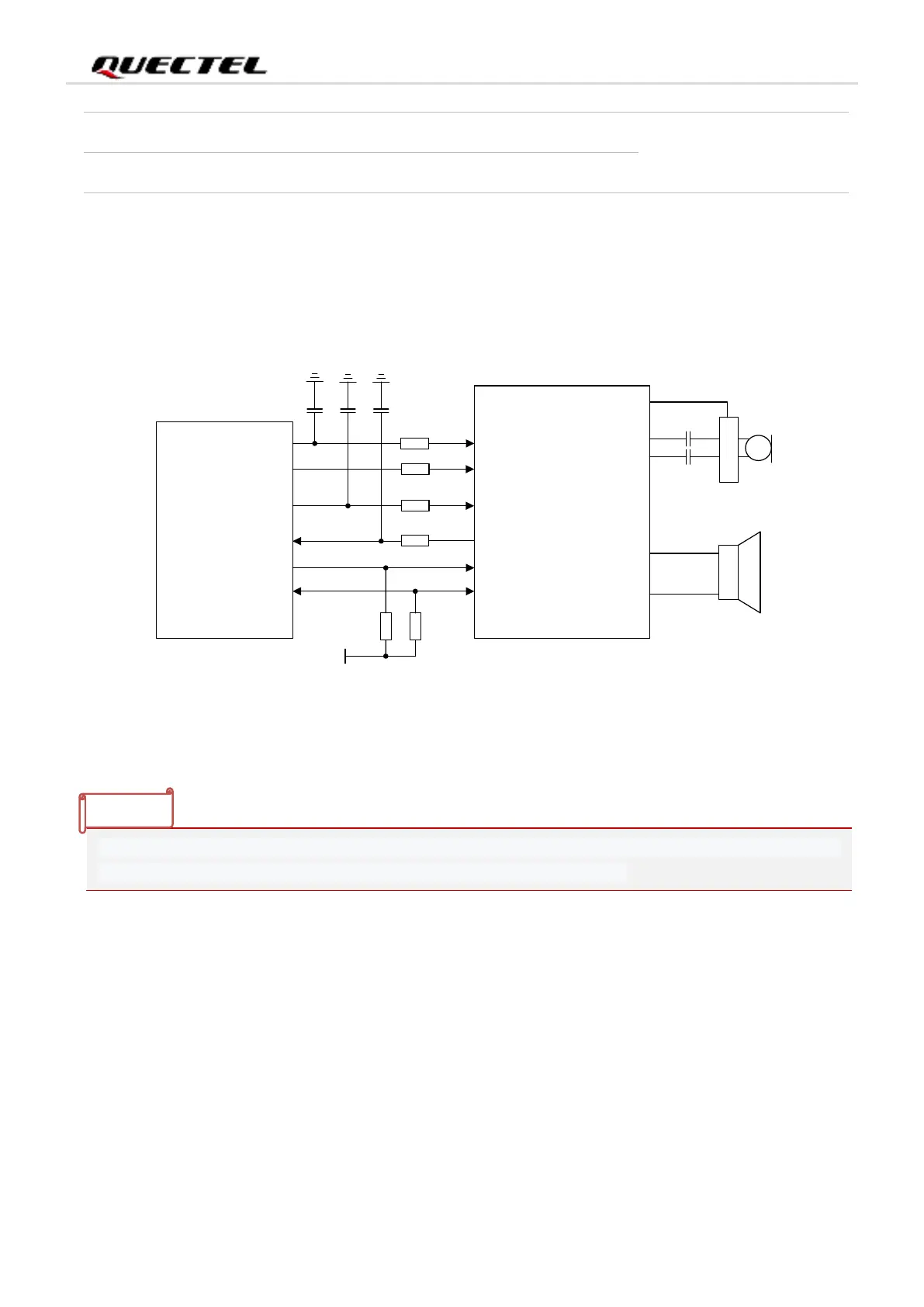

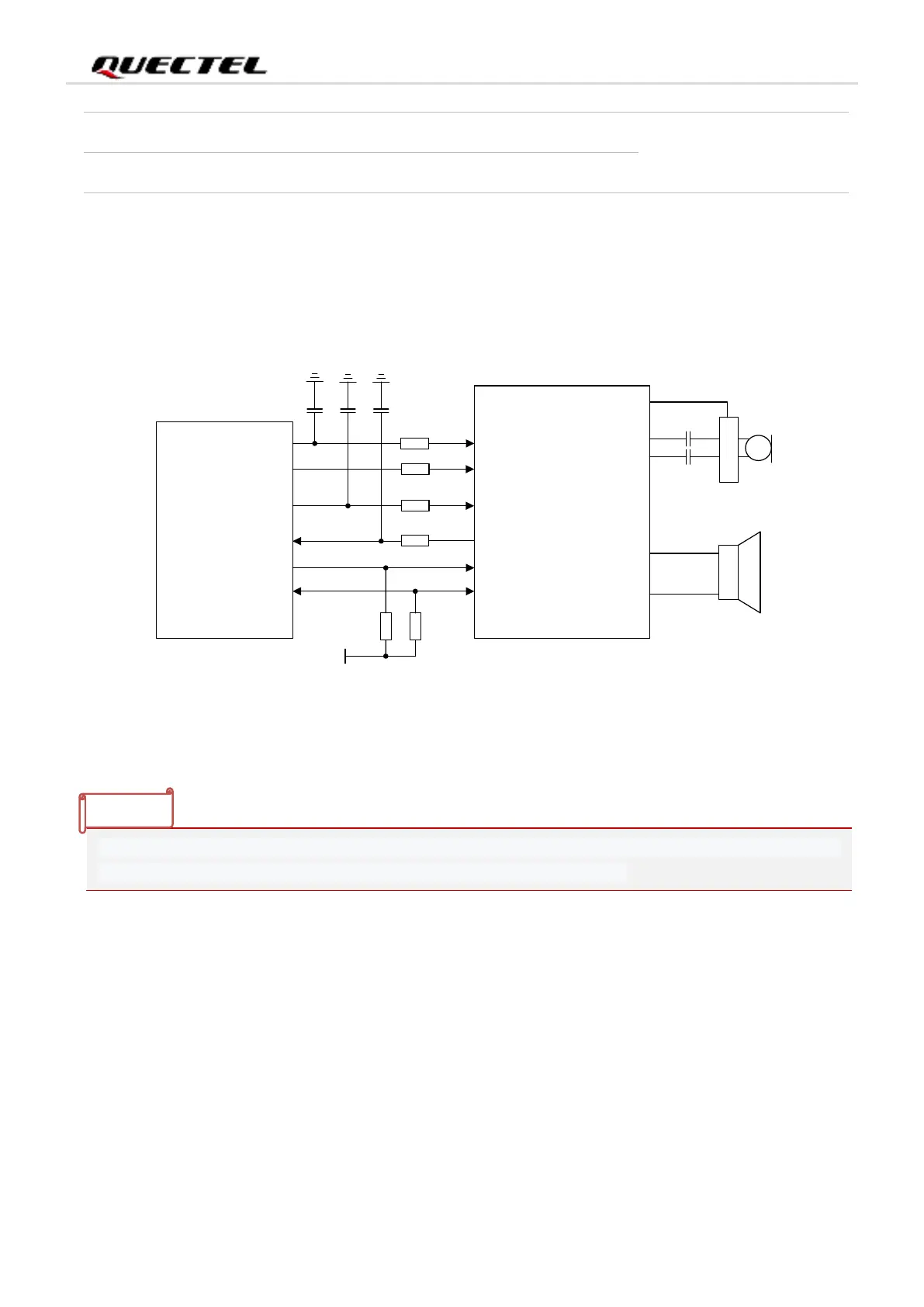

The following is a reference design for the PCM and I2C interfaces with external Codec chip

PCM_DIN

PCM_DOUT

PCM_SYNC

PCM_CLK

I2C_SCL

I2C_SDA

Module

1.8 V

4.7K

4.7K

BCLK

LRCK

DAC

ADC

SCL

SDA

BIAS

MICBIAS

INP

INN

LOUTP

LOUTN

Codec

22R

33 pF

22R

22R

33 pF

22R

33 pF

Figure 22: PCM and I2C Interface Circuit Reference Design

Used for external codec.

An external 1.8 V pull-up

resistor is needed.

It is recommended to reserve the RC (R = 22 Ω, C = 33 pF) circuit on the PCM signal line and the

capacitor should be placed close to the module, especially on PCM_CLK.

Loading...

Loading...