R8C/1A Group, R8C/1B Group 14. Timers

Rev.1.30 Dec 08, 2006 Page 115 of 315

REJ09B0252-0130

14.1.3 Event Counter Mode

In event counter mode, external signal inputs to the INT1/CNTR0 pin are counted (refer to Table 14.4 Event

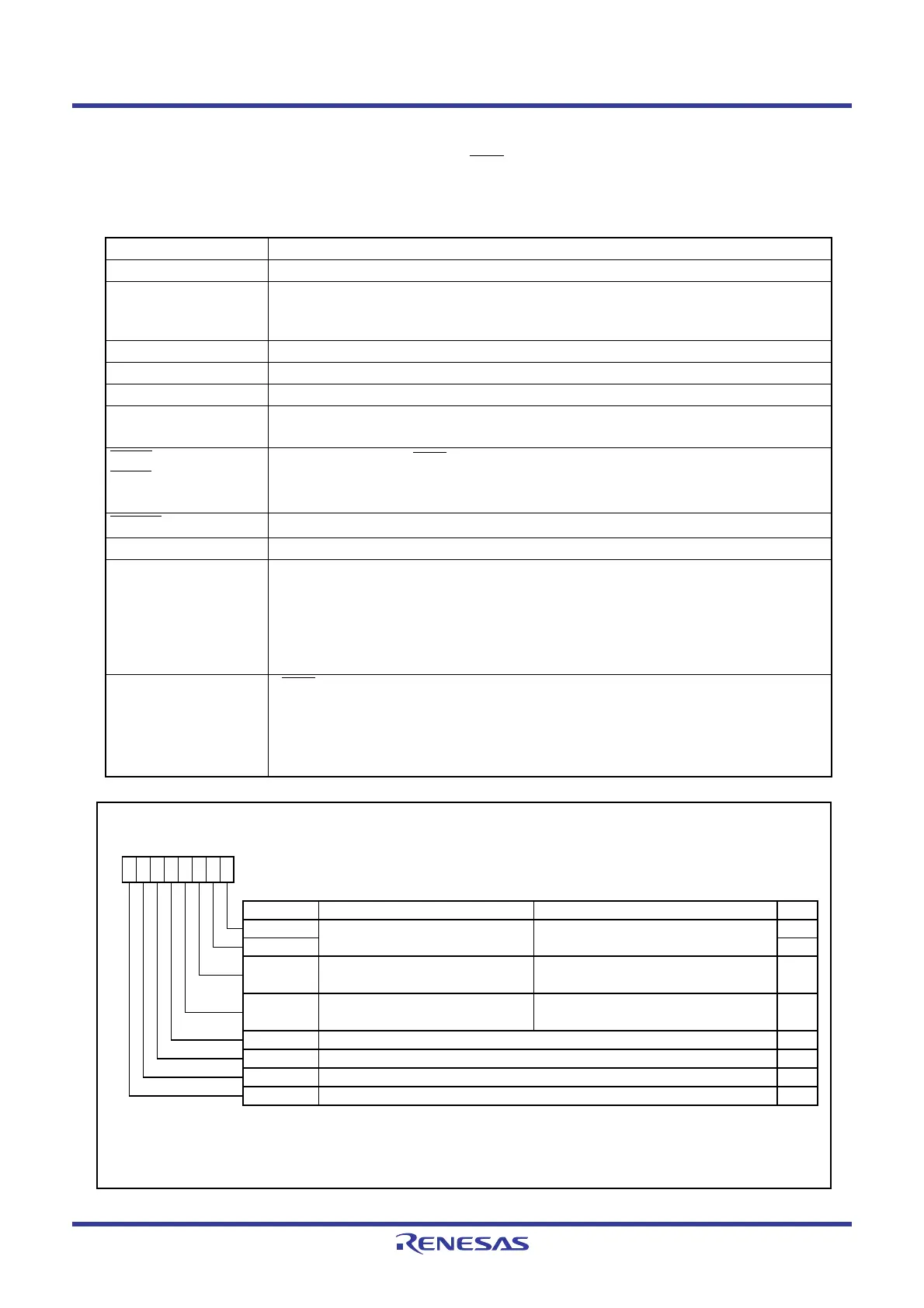

Counter Mode Specifications). Figure 14.6 shows the TXMR Register in Event Counter Mode.

Figure 14.6 TXMR Register in Event Counter Mode

Table 14.4 Event Counter Mode Specifications

Item Specification

Count source External signal which is input to CNTR0 pin (Active edge selectable by software)

Count operations • Decrement

• When the timer underflows, the contents of the reload register are reloaded and

the count is continued.

Divide ratio 1/(n+1)(m+1) n: value set in PREX register, m: value set in TX register

Count start condition 1 (count starts) is written to the TXS bit in the TXMR register.

Count stop condition 0 (count stops) is written to the TXS bit in the TXMR register.

Interrupt request

generation timing

• When timer X underflows [timer X interrupt]

INT10

/CNTR00,

INT11

/CNTR01

pin functions

Count source input

(INT1

interrupt input)

CNTR0

pin function

Programmable I/O port

Read from timer The count value can be read out by reading registers TX and PREX.

Write to timer • When registers TX and PREX are written while the count is stopped, values are

written to both the reload register and counter.

• When registers TX and PREX are written during the count, the value is written

to each reload register of registers TX and PREX at the following count source

input, the data is transferred to the counter at the second count source input,

and the count re-starts at the third count source input.

Select functions

•INT1

/CNTR0 signal polarity switch function

The R0EDG bit can select the active edge of the count source.

• Count source input pin select function

The CNTRSEL bit in the UCON register can select the CNTR00 or CNTR01

pin.

Timer X Mode Register

Symbol Address After Reset

TXMR

008Bh 00h

Bit Symbol Bit Name Function RW

INT1

____

/CNTR0 signal

polarity switch bit

(1)

NOTES :

1.

2.

Set to 0 in event counter mode.

RW

TXUND RW

TXEDG

Set to 0 in event counter mode.TXMOD2

RW

b3 b2

0 : Rising edge

1 : Falling edge

TXS

Timer X count start flag

(2)

0 : Stops counting.

1 : Starts counting.

b1

Set to 0 in event counter mode.

b0

0000

b7 b6 b5 b4

TXMOD0 RWOperating mode select bits 0, 1

b1 b0

1 0 : Event counter mode

TXMOD1 RW

Set to 0 in event counter mode.

Refer to

14.1.6 Notes on Timer X

for precautions regarding the TXS bit.

01

The IR bit in the INT1IC register may be set to 1 (requests interrupt) w hen the R0EDG bit is rew ritten.

Refer to

12.5.5 Changing Interrupt Sources

.

R0EDG RW

RW

TXOCNT RW

Loading...

Loading...