R8C/1A Group, R8C/1B Group 15. Serial Interface

Rev.1.30 Dec 08, 2006 Page 167 of 315

REJ09B0252-0130

15.2.2 Bit Rate

In UART mode, the bit rate is the frequency divided by the UiBRG (i = 0 or 1) register.

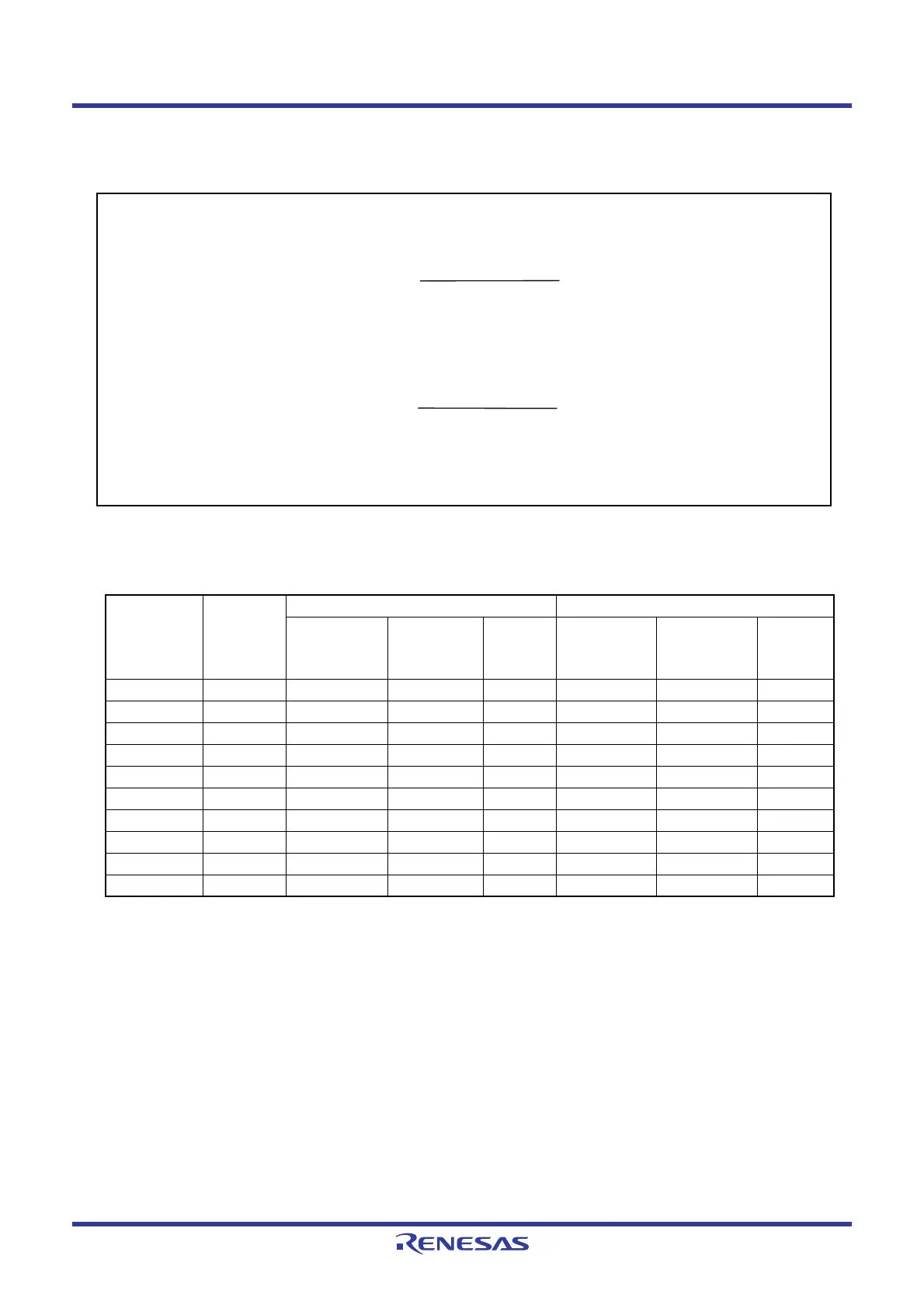

Figure 15.12 Calculation Formula of UiBRG (i = 0 or 1) Register Setting Value

i = 0 or 1

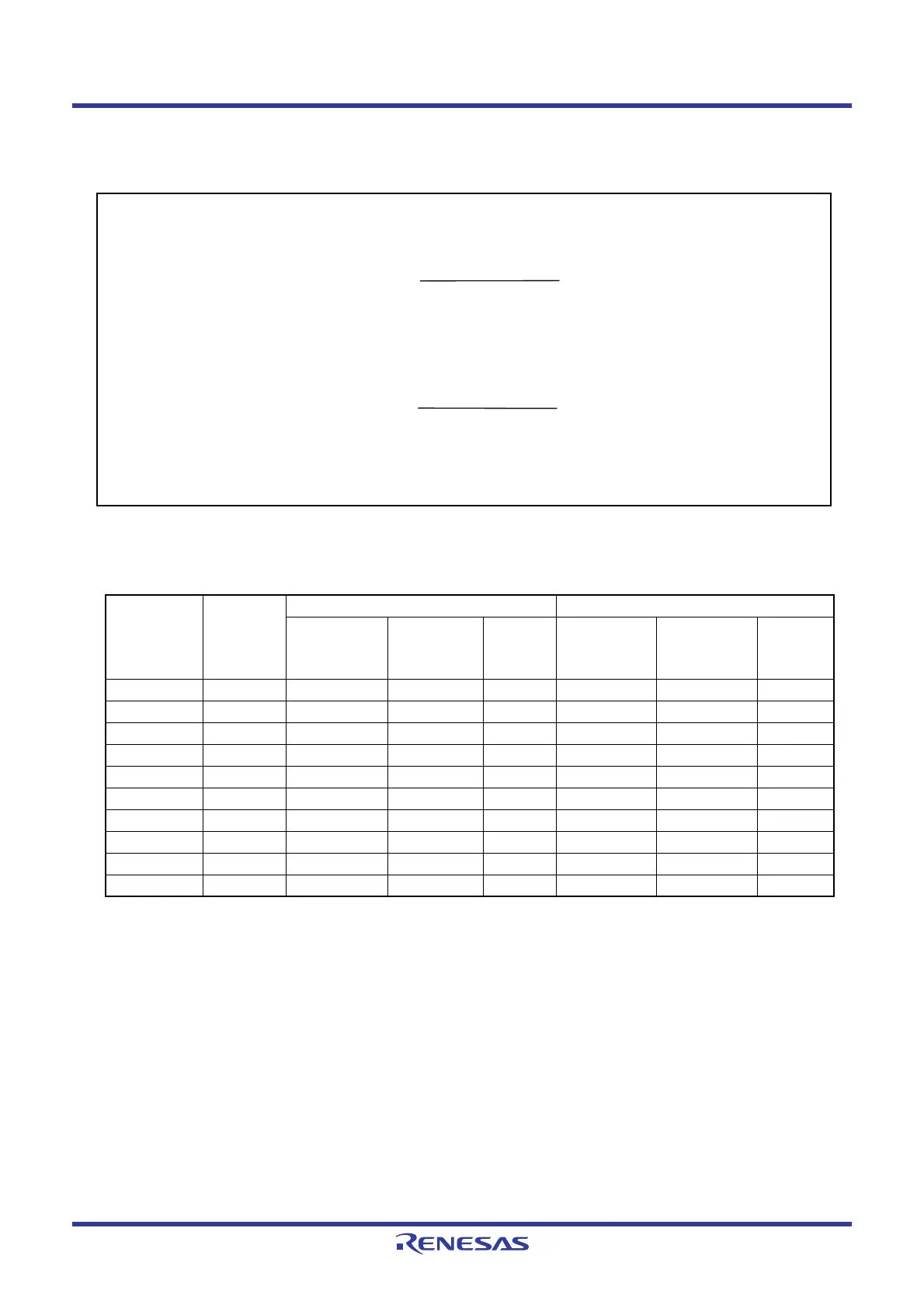

Table 15.7 Bit Rate Setting Example in UART Mode (Internal Clock Selected)

Bit Rate

(bps)

BRG

Count

Source

System Clock = 20 MHz System Clock = 8 MHz

UiBRG

Setting Value

Actual Time

(bps)

Error (%)

UiBRG

Setting

Value

Actual

Time (bps)

Error (%)

1200 f8 129(81h) 1201.92 0.16 51(33h) 1201.92 0.16

2400 f8 64(40h) 2403.85 0.16 25(19h) 2403.85 0.16

4800 f8 32(20h) 4734.85 -1.36 12(0Ch) 4807.69 0.16

9600 f1 129(81h) 9615.38 0.16 51(33h) 9615.38 0.16

14400 f1 86(56h) 14367.82 -0.22 34(22h) 14285.71 -0.79

19200 f1 64(40h) 19230.77 0.16 25(19h) 19230.77 0.16

28800 f1 42(2Ah) 29069.77 0.94 16(10h) 29411.76 2.12

31250 f1 39(27h) 31250.00 0.00 15(0Fh) 31250.00 0.00

38400 f1 32(20h) 37878.79 -1.36 12(0Ch) 38461.54 0.16

51200 f1 23(17h) 52083.33 1.73 9(09h) 50000.00 -2.34

UART Mode

• Internal clock selected

UiBRG register setting value =

fj

Bit Rate

× 16

- 1

Fj: Count source frequency of the UiBRG register (f1, f8, or f32)

• External clock selected

fEXT

Bit Rate

× 16

- 1

fEXT : Count source frequency of the UiBRG register (external clock)

UiBRG register setting value =

i = 0 or 1

Loading...

Loading...