Table 4: Switching Characteristics (cont'd)

Symbol Description Conditions Min. Max. Unit

T

CHU

Cable Hold Time (TDO relative to the negative

edge of TCK)

V

REF

= 1.2V to 3.3V 1 - ns

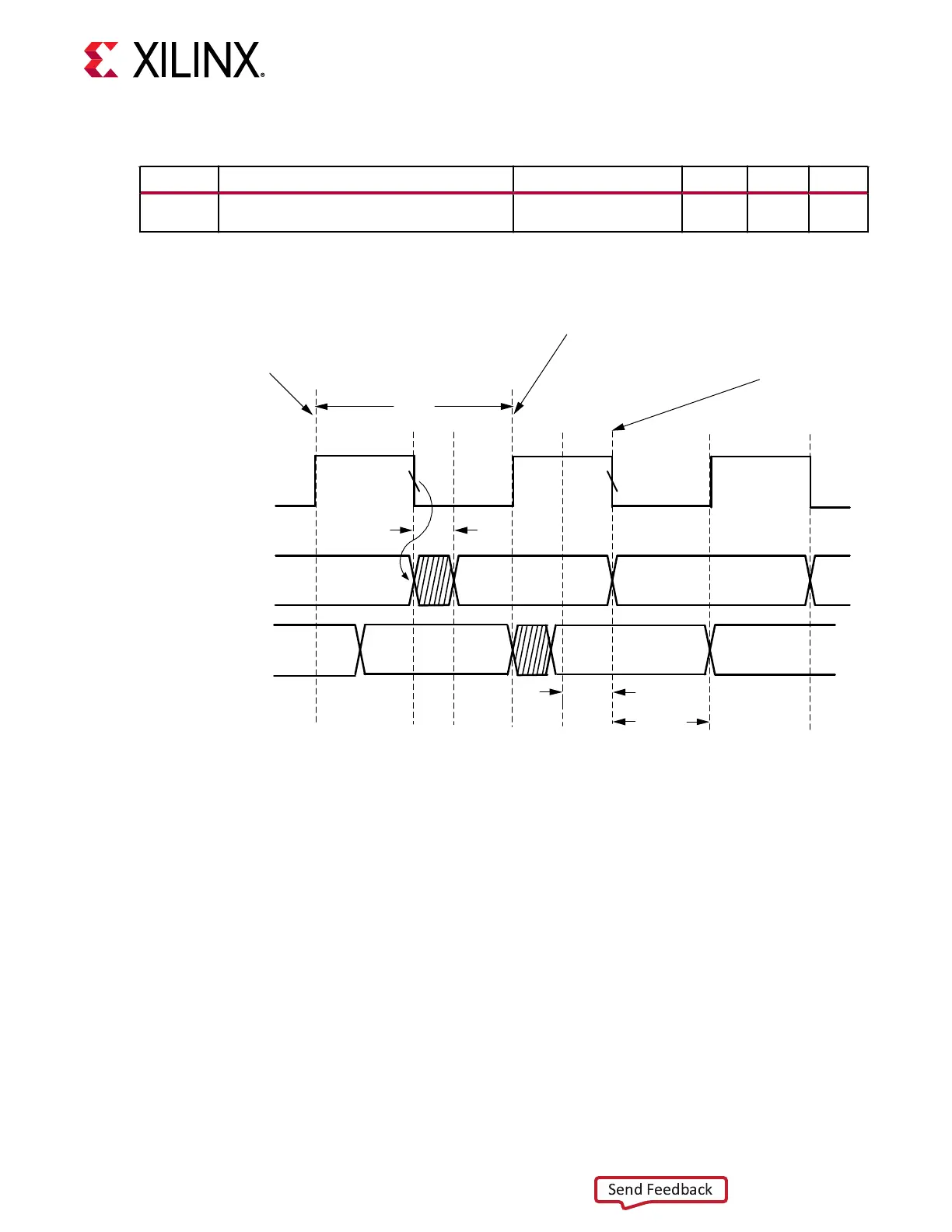

Figure 8: SmartLynq+ Module Timing Diagram

Target devices sample TMS and TDI

on the rising edge of TCK

T

CLK

T

TSU

T

CPD

TCK

TMS

TDI

SmartLynq+ Module

asserts TMS and TDI

on the falling edge of TCK

Target device asserts TDO

on the falling edge of TCK

TDO

T

CHU

X25128-021621

Chapter 7: JTAG Target Interface

UG1514 (v1.0) March 8, 2021 www.xilinx.com

SmartLynq Module+ 24

Loading...

Loading...