assigned to RST_LKOUT input of both the trip logic to enable external reset with a

push button. Three other trip logics TRPPTRC3...4 are also available if the IED is

ordered with high speed binary outputs options.

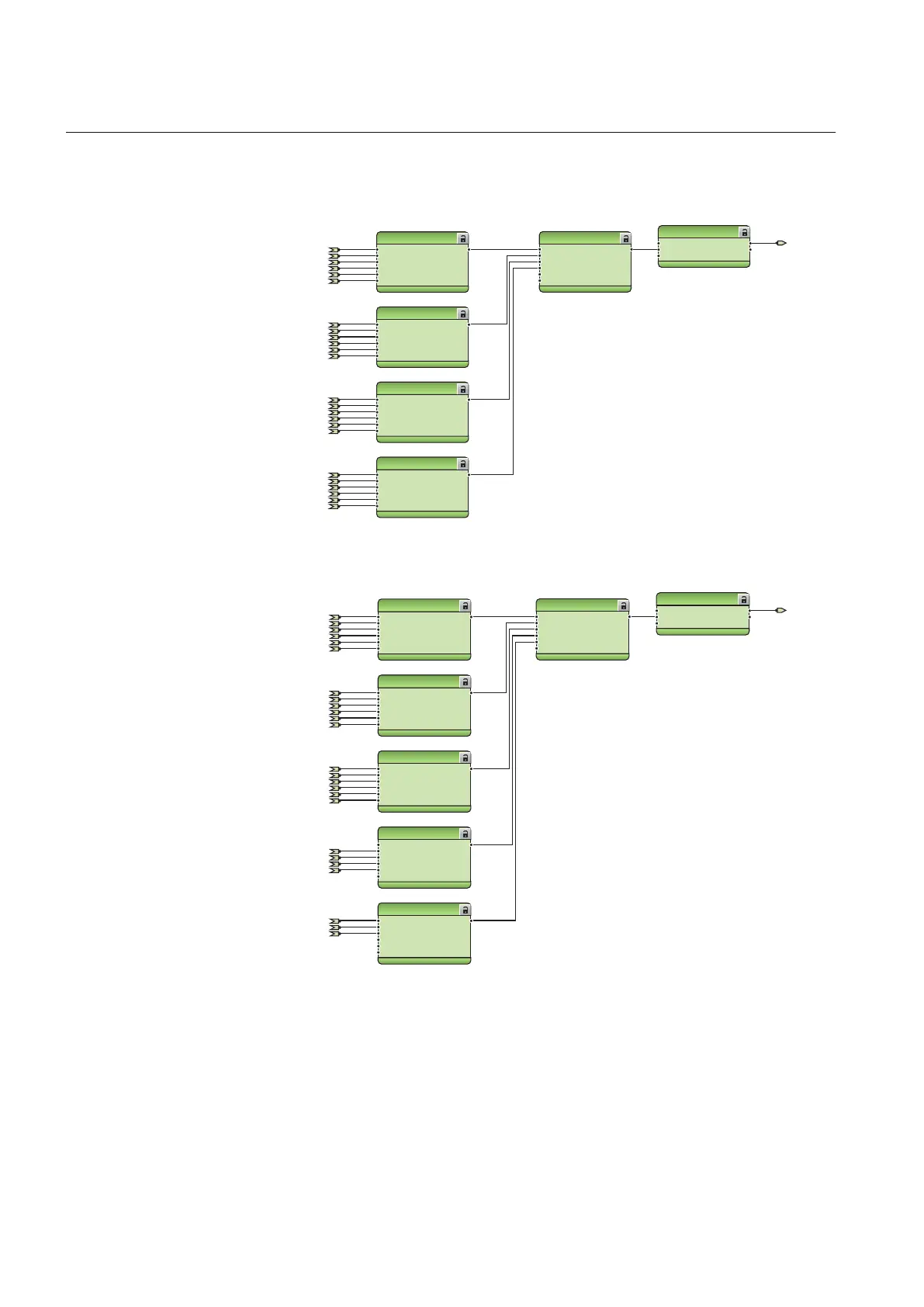

TRPPTRC1

BLOCK

OPERATE

RST_LKOUT

TRIP

CL_LKOUT

OR6

B1

B2

B3

B4

B5

B6

O

OR6

B1

B2

B3

B4

B5

B6

O

OR6

B1

B2

B3

B4

B5

B6

O

OR6

B1

B2

B3

B4

B5

B6

O

OR6

B1

B2

B3

B4

B5

B6

O

TRPPTRC1_TRIP

PHIPTOC1_OPERATE

PHLPTOC1_OPERATE

PHHPTOC1_OPERATE

NSPTOC1_OPERATE

PHHPTOC2_OPERATE

NSPTOC2_OPERATE

EFPADM1_OPERAT E

EFPADM2_OPERAT E

EFPADM3_OPERAT E

INTRPTEF1_OPERATE

PDNSPTOC1_OPERATE

ROVPTOV1_OPERATE

ROVPTOV2_OPERATE

ROVPTOV3_OPERATE

DEFHPDEF1_OPERATE

DEFLPDEF1_OPERATE

DEFLPDEF2_OPERATE

EFHPTOC1_OPERATE

WPWDE1_OPERATE

WPWDE2_OPERATE

WPWDE3_OPERATE

ARCSARC1_OPERATE

ARCSARC2_OPERATE

ARCSARC3_OPERATE

GUID-AF22589C-B208-45F8-ADB9-D925C183367A V1 EN

Figure 69: Trip logic TRPPTRC1

OR6

B1

B2

B3

B4

B5

B6

O

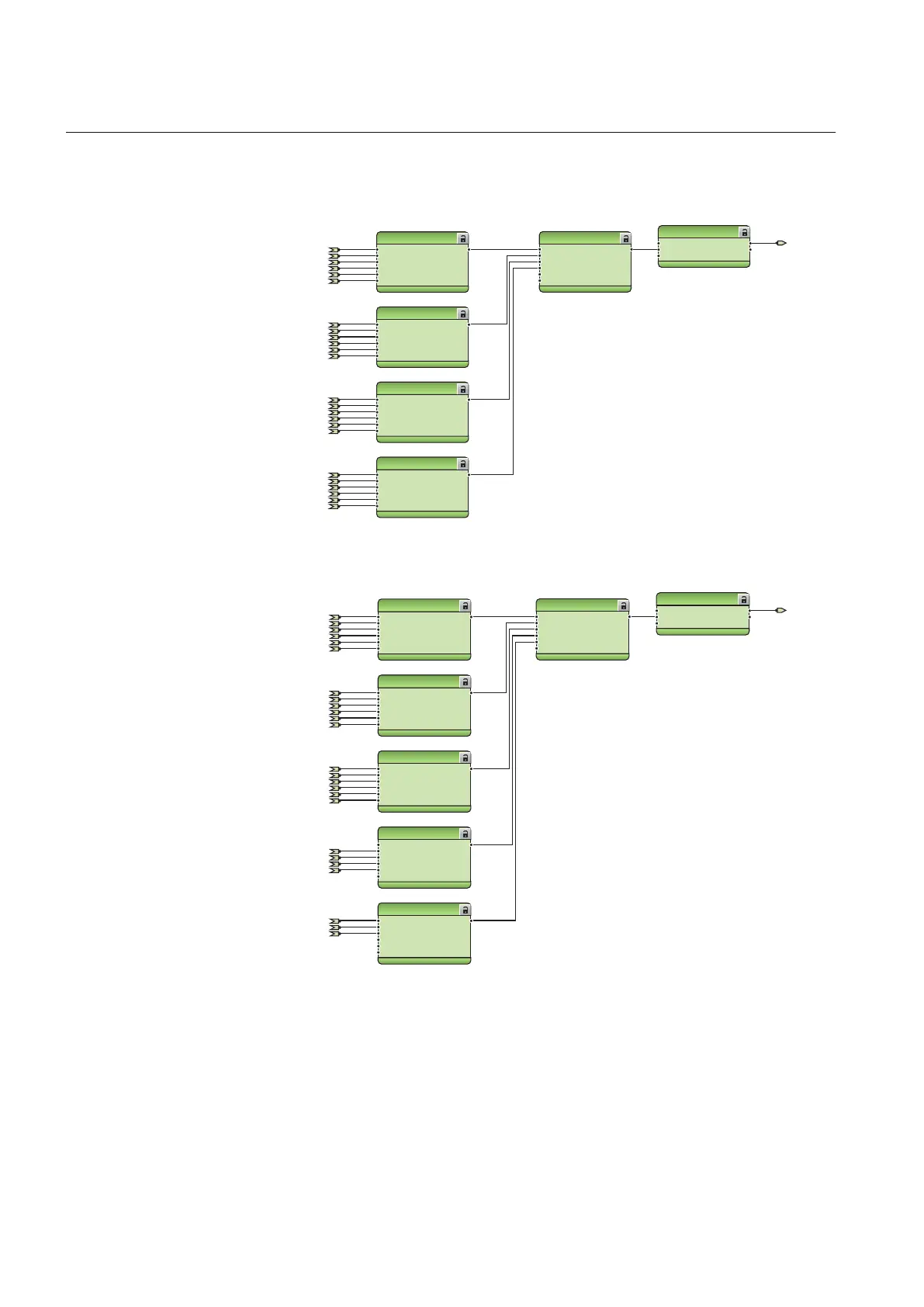

TRPPTRC2

BLOCK

OPERATE

RST_LKOUT

TRIP

CL_LKOUT

OR6

B1

B2

B3

B4

B5

B6

O

OR6

B1

B2

B3

B4

B5

B6

O

OR6

B1

B2

B3

B4

B5

B6

O

OR6

B1

B2

B3

B4

B5

B6

O

OR6

B1

B2

B3

B4

B5

B6

O

TRPPTRC2_TRIP

PHIPTOC1_OPERATE

PHLPTOC1_OPERATE

PHHPTOC1_OPERATE

NSPTOC1_OPERATE

PHHPTOC2_OPERATE

NSPTOC2_OPERATE

EFPADM1_OPERATE

EFPADM2_OPERATE

EFPADM3_OPERATE

INTRPTEF1_OPERATE

PDNSPTOC1_OPERATE

ROVPTOV1_OPERATE

ROVPTOV2_OPERATE

ROVPTOV3_OPERATE

DEFHPDEF1_OPERATE

DEFLPDEF1_OPERATE

DEFLPDEF2_OPERATE

EFHPTOC1_OPERATE

WPWDE1_OPERATE

WPWDE2_OPERATE

WPWDE3_OPERATE

ARCSARC1_OPERATE

ARCSARC2_OPERATE

ARCSARC3_OPERATE

CCBRBRF1_TRRET

GUID-1D960595-DAB7-44B3-8D6A-36CB54AAFCB6 V1 EN

Figure 70: Trip logic TRPPTRC2

3.4.3.2 Functional diagrams for disturbance recorder

The START and OPERATE outputs from the protection stages are routed to trigger the

disturbance recorder or, alternatively, only to be recorded by the disturbance recorder

Section 3 1MRS756378 S

REF615 standard configurations

86 REF615

Application Manual

Loading...

Loading...