81

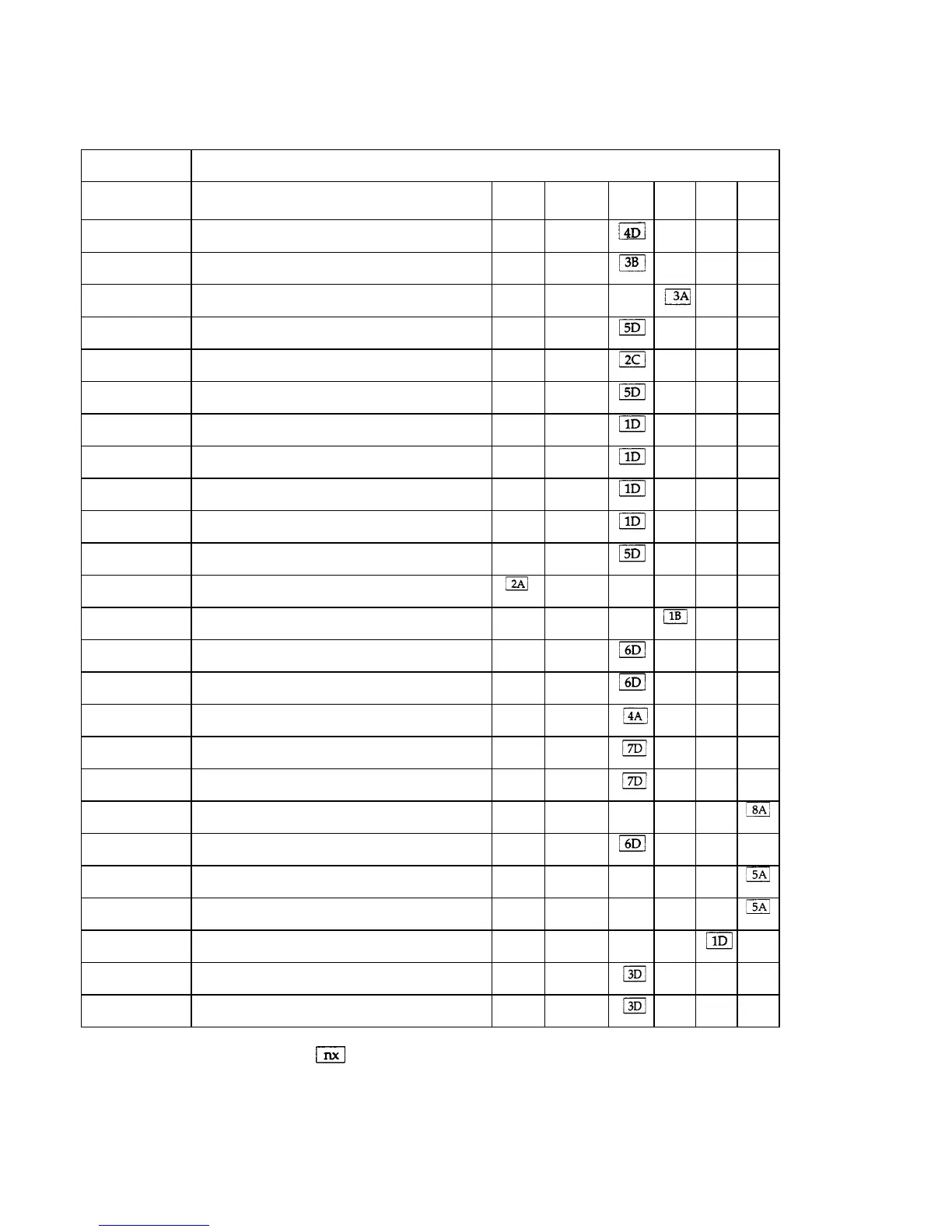

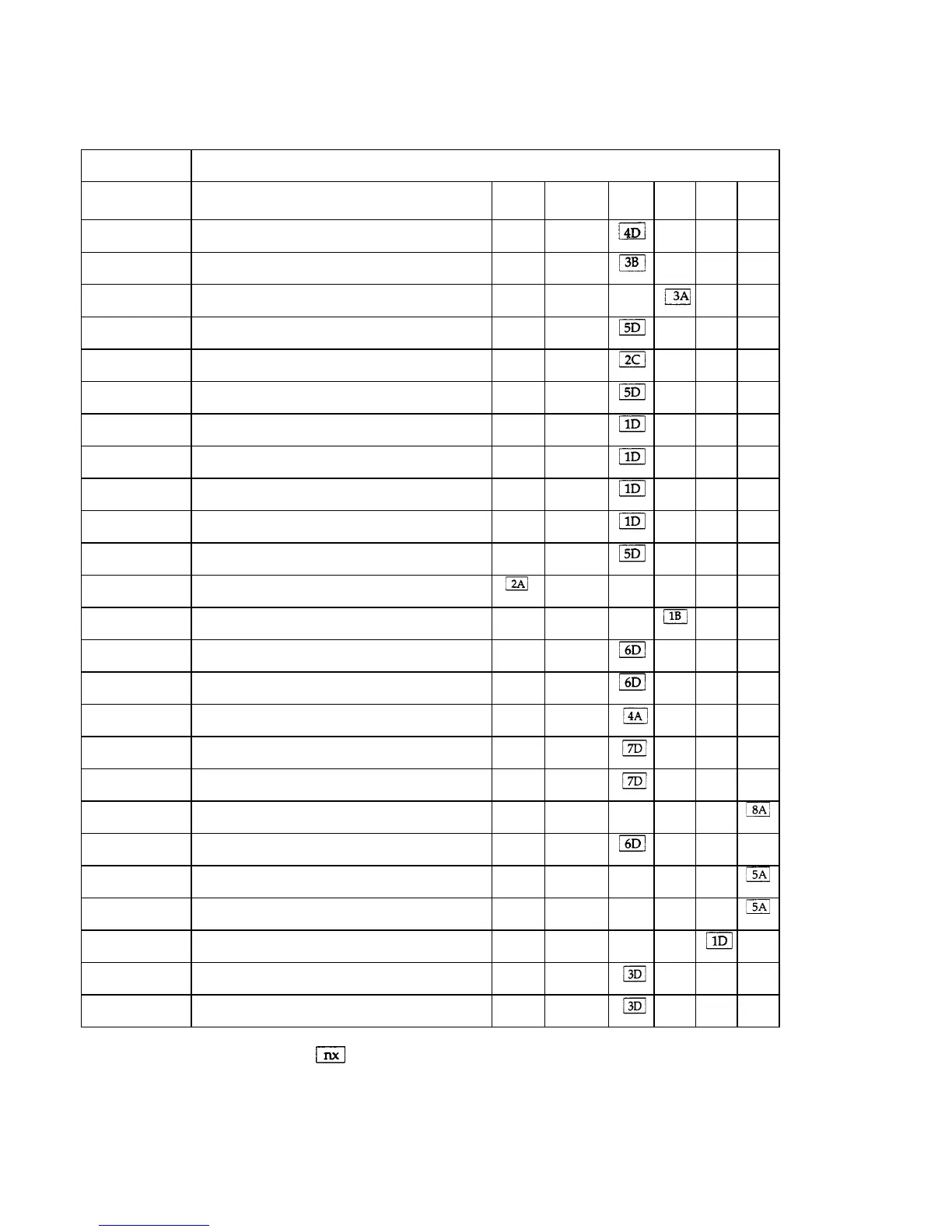

Table 6-2. Schematic Diagram, Inter-Sheet Signal Connections

Signal Sheet and Coordinates

Mnemonic Function

1

123456

ACLR* Analog circuits clear (D) 1A

CC_PROG Programming voltage for CC mode (A) 8C

CCVTST Comparator output, main DAC self-test (D) 6D

CG*

1 k/10 k

Ω range select (D)

4D

CV_PROG Programming voltage for CV mode (A) 7D

CR*

1

Ω range select (D)

3C 8D

CS0* Main DAC chip select (D) 8D

CS1* Transient DAC chip select (D) 7C

CS3* Readback DAC chip select (D) 8B

CS4* Select secondary data bus buffer latch (D) 8D

DAC_REF* Main DAC CC/CV reference enable (D) 3C

EEPON* EEPROM power-on disable (D) 2A

EXT_PROG External programming (A) from (TB301-6)

FAN1 Fan speed control bit (D) 3C

FAN2 Fan speed control bit (D) 3C

HIGH* Enable transient DAC output (D) 8C

H/L* Main DAC transfer control (D) 8D

H/L_AD Readback DAC transfer control (D) 8B

IMON* Input current monitor (A) 3D 6B

IMONR Current monitor comparator output (D) 3A

+IN Input bus (A) (binding post +) 8A

-IN Input bus (A) (binding post -) 8A

IPROG Power driver programming signal (A) 8D

BO* Brown-out status (D) 8B

OP* Overpower status (D) 8A

1

(A) = analog (D) = digital = signal origin

Loading...

Loading...