82

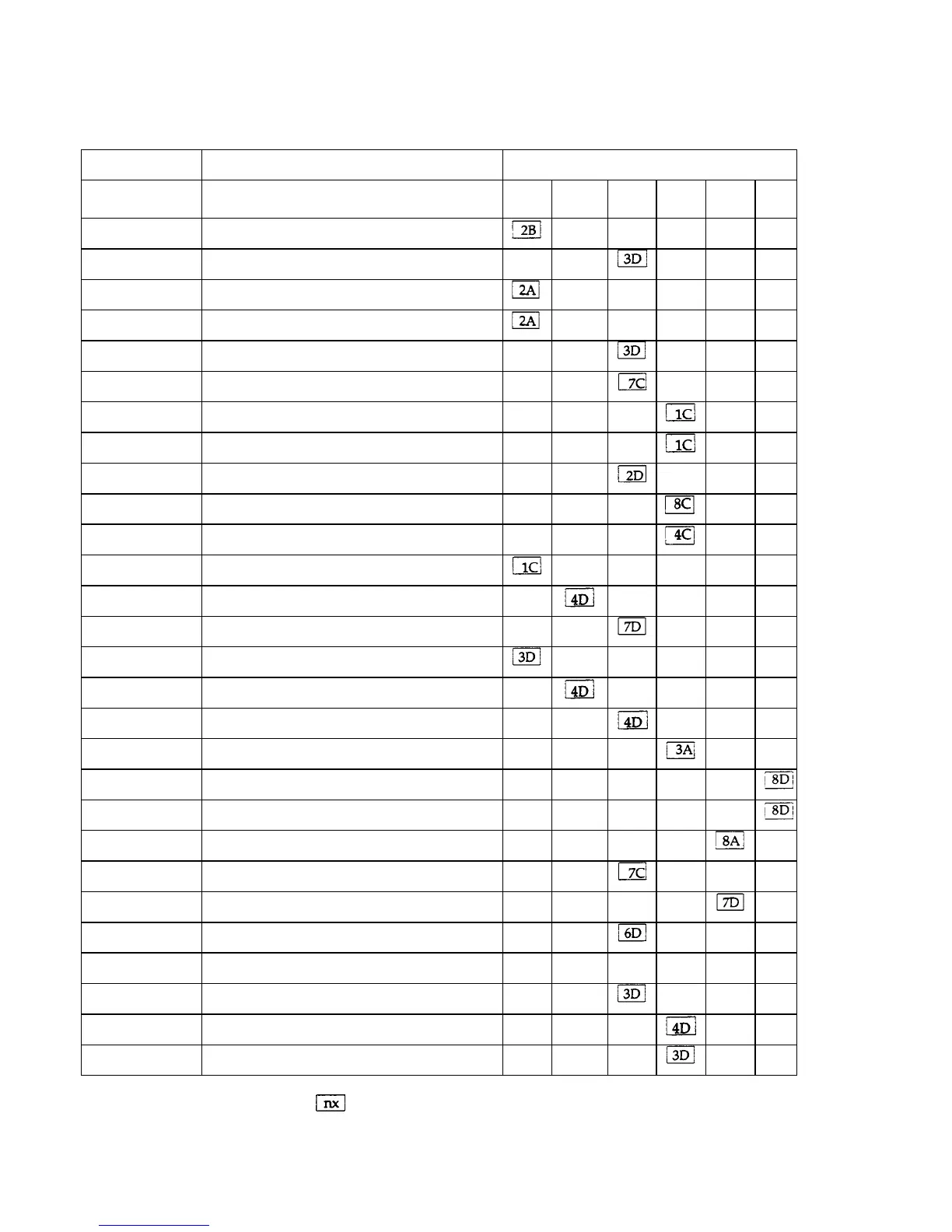

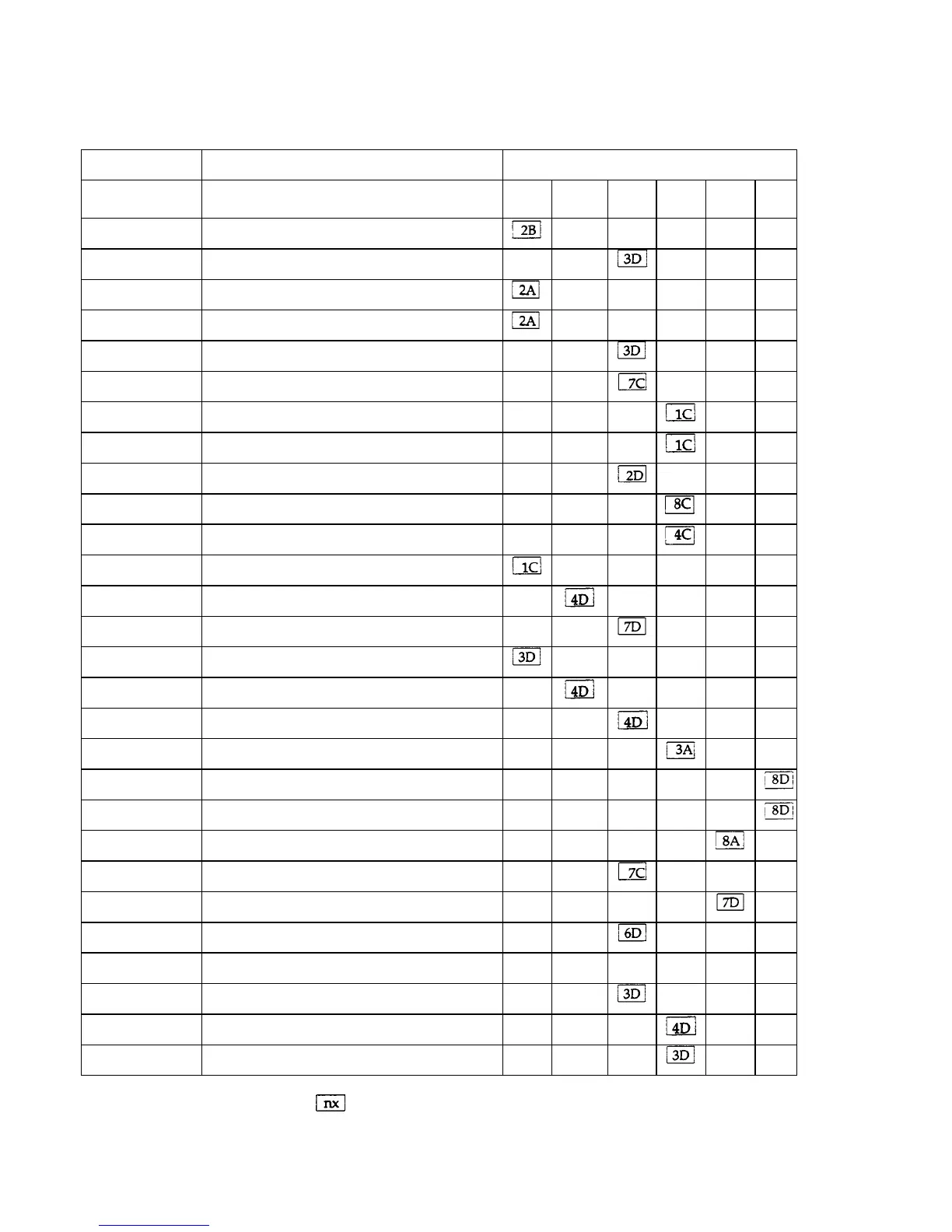

Table 6-2. Schematic Diagram, Inter-Sheet Signal Connections (continued)

Signal Sheet and Coordinates

Mnemonic Function

1

123456

OPTO_PCLR* Opto couplers power-on disable (D) 5D

OV* Overvoltage status (D) 8B

PCLR Primary power-on clear (D) 6A

PCLR* Primary power-on clear (D) 4A

PORT PORT output (D) 1B

RNG Range select (D) 8C

+S Input bus +sense (A) from (TB301-1) 1D

- S Input bus - sense (A) from (TB301-2) 1D

SD(0:7) Data bus (D) 8C

SDB(0:7) Buffered data bus (D) 8C

SLEW Slew programming reference voltage (A) 6B

SPCLR* Secondary power-on clear (D) 7D 8D 1B

SRX Secondary processor receiver (D) 8D

STX Secondary processor transmitter (D) 4C

TEMP Temperature reference (A) 5A

TRIG Trigger (D) 6A 8D

TRIG_EN* Main DAC trigger enable (D) 8D

TMONR Temperature monitor comparator output (D) 6D

TURNON Power-on output disable (D) 1B

UNREG Input to overshoot circuits (A) 8A

UNREG* Output of unregulated-output comparator (D) 3D

UXFER Main & Transient DACs transfer control (D) 8D

VMON* Input voltage monitor (A) 3C

VMONR Voltage monitor comparator output (D) 3A

VOFF Voltage off 4C 8D

VOLT_FLT Over or reverse voltage fault state (D) lB

-10 VREF 10 volts reference 3D

+ 12 VREF 12 volts reference 5B

1

(A) = analog (D) = digital = signal origin

Loading...

Loading...