Chapter 14 High Speed Counter Module AS02HC

14-11

Pulse Input Counting

To perform the pulse-input counting, first set the configuration of channels, which includes pulse type and counter type

selection in HWCONFIG. If the counter type is set to the linear counter, the maximum counting value and minimum counting

value need be set. After the configuration setting is completed, use the API instruction DHCCNT which is special for

AS02HC-A in a program to obtain the counting value, achieve the counter control as well as get the real time counter state.

1. Pulse Type

Specify the pulse input type which can be A/B phase (2x), A/B phase (4x), CW/CCW or pulse + direction.

Pulse Type

A/B phase (4x),

CW/CCW,

- A/B phase (2x)

2. Using the ring counter

The ring counter value is cyclical in the range of -2,147,483,648 to 2,147,483,647. When it is greater than

2,147,483,647, the count value changes to -2,147,483,648 and then the counting continues. When it is less than -

2,147,483,648, the count value changes to 2,147,483,647 and then the counting continues.

0

2

,147,483,647

-2,147,483,648

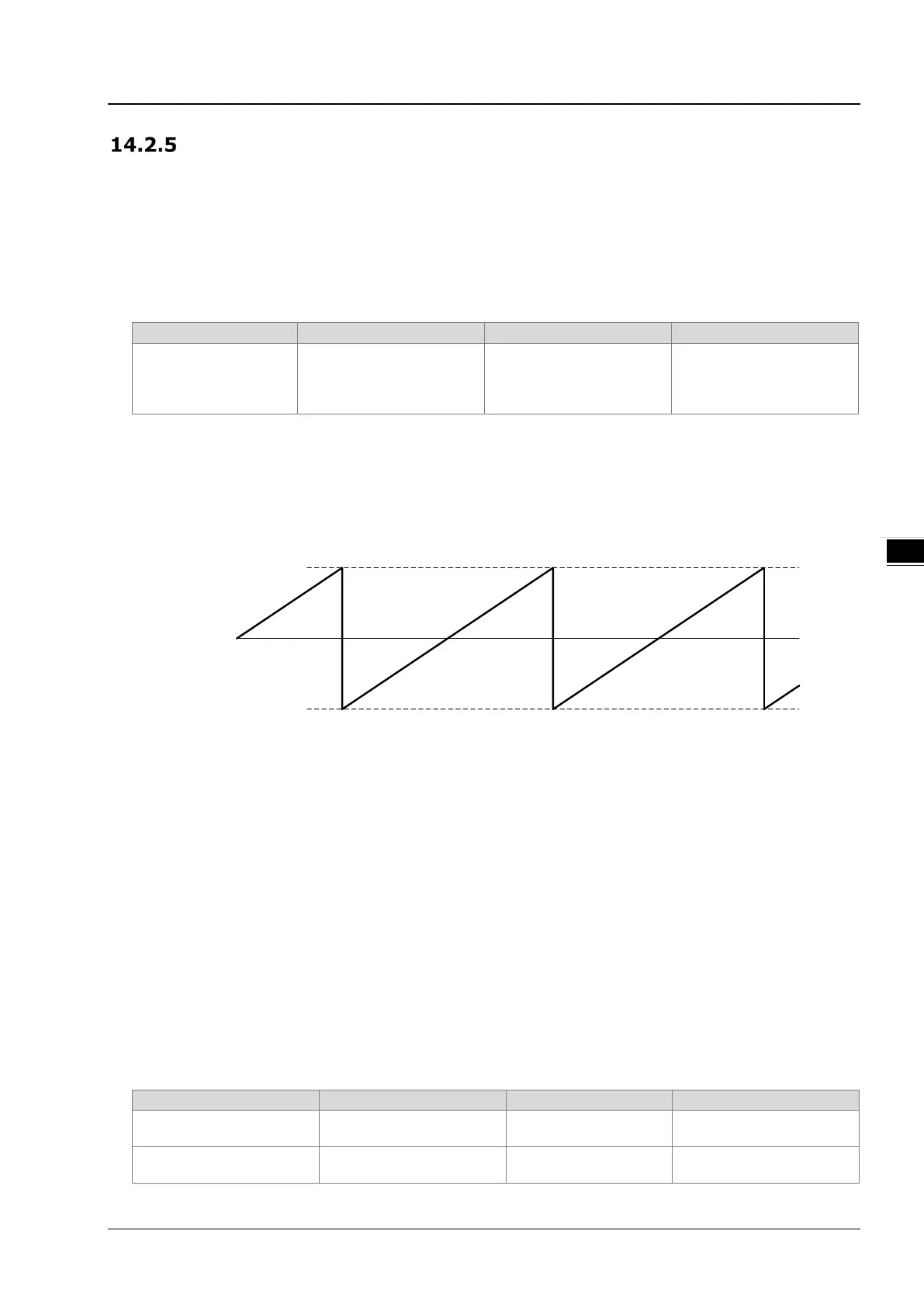

3. Using the linear counter

The maximum and minimum counter values must be set up. The counter counts up and down between the two limit

counter value. When the count value exceeds the maximum value, the counter state will show the warning of “The

value exceeds the range!” and the count value will be fixed at the maximum counter value. When the count value is

below the minimum value, the counter state will show the warning of “The value exceeds the range!” and the count

value will be fixed at the minimum counter value.

When the count value is beyond the allowed range, the counting persists internally in the hardware. The counter

returns to normal and the count value is refreshed when the internal count value comes back within the valid range.

But when the internal count value in the hardware is beyond the valid range of -2,147,483,648 to 2,147,483,647, the

counter state shows linear counter overflow or linear counter underflow, the counting stops and the internal count

value stops at 2,147,483,647 or -2,147,483,648. The counting can not continue until the count value overflow state of

the counter is cleared.

The methods to clear the states include resetting the counter through phase-Z inputs, executing Reset/Preset via

DHCCNT instruction, disabling DHCCNT instruction or changing the CPU from RUN to STOP.

Max. counter value

(upper limit)

0 ~ 2147483647 - 2147483647

Min. counter value

(lower limit)

-2147483648 ~ 0 - -2147483648

Loading...

Loading...