Intel

®

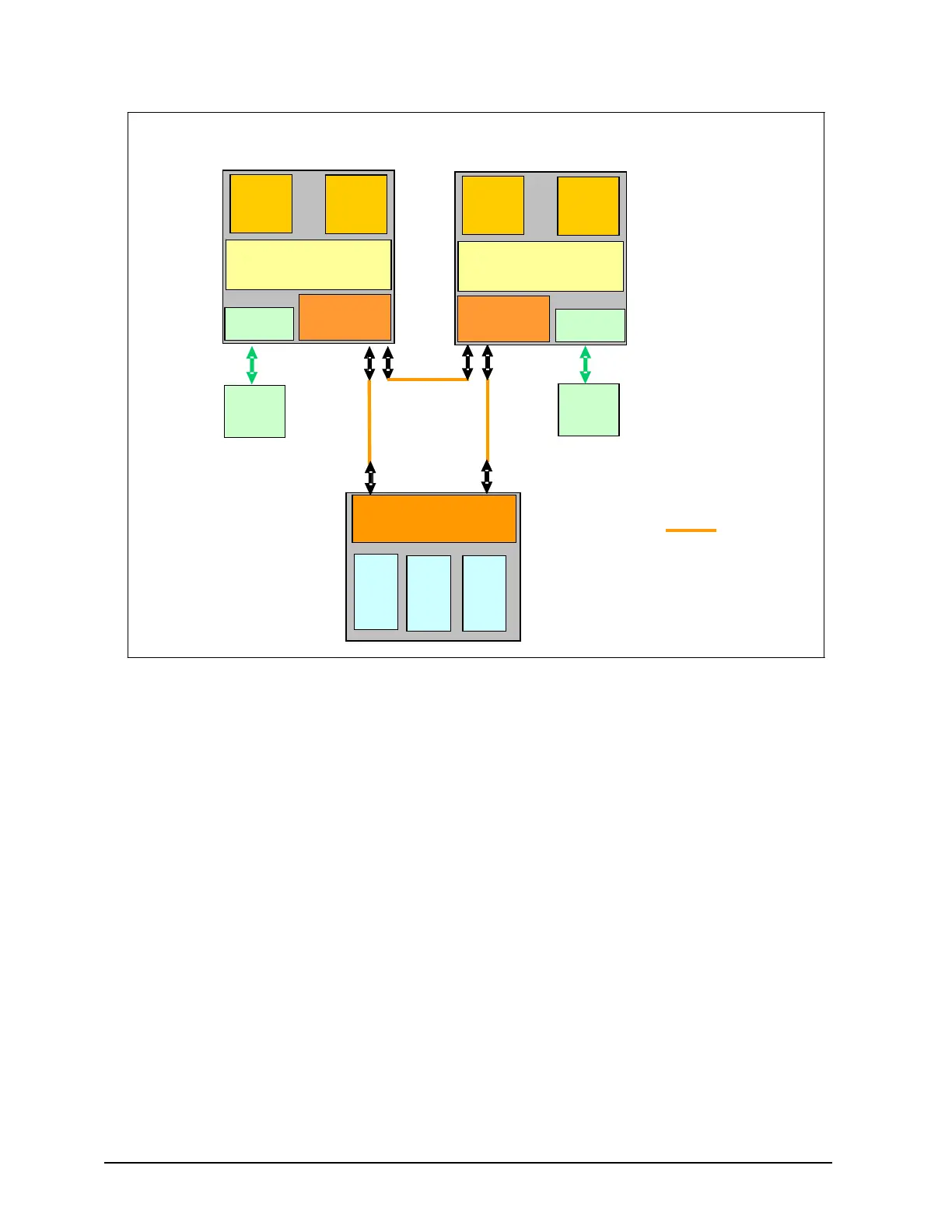

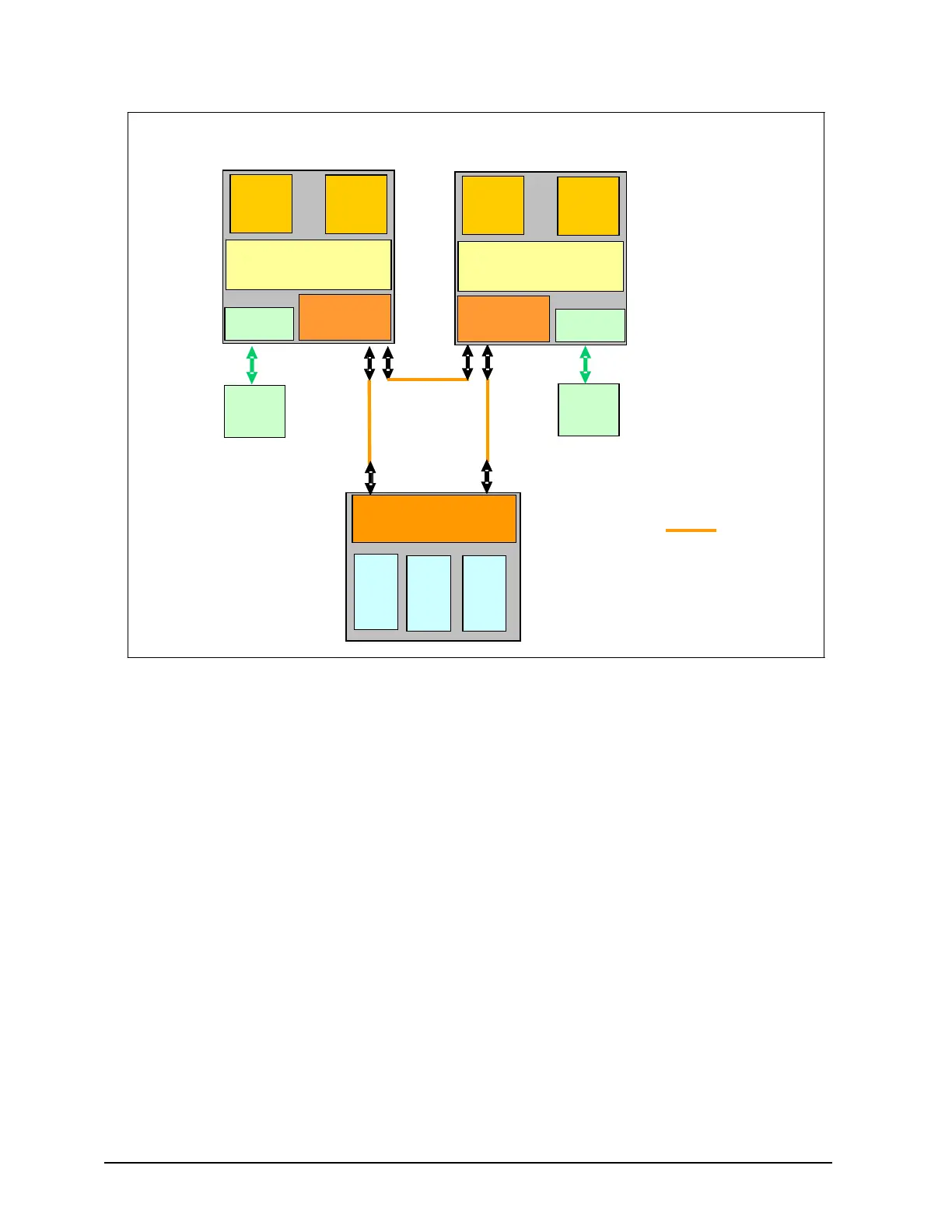

Server Board S5500BC TPS Functional Architecture

Revision 1.0 Intel order number: E42249-003 17

Intel

®

Xeon

®

5500 processor

Intel

®

Xeon

®

5500 processor

Core

0

…

Co

e

3

Co

e

0

…

Co

e

3

Cache

Cache

Mem

I/F

CSI

Inte

face

CSI Inte

face

Mem I

F

Memo

y

Memo

y

CSI

Interface

CSI

Link

PC

-E

PC

-E PC

-E

Intel® 5500

I/O Hub

Figure 13. Intel

®

IOH 5500 Chipset with Intel

®

QuickPath Interconnect Block Diagram

3.1.2 Processor Population Rules

When using a single processor configuration, you must install the processor into the processor

socket labeled CPU_1. A terminator is not required in the second processor socket when a

single processor is used.

When two processors are installed, the following population rules apply:

Both processors must be from the same processor family.

Both processors must have the same Intel

®

QuickPath Interconnect speed.

Both processors must have the same cache size.

Processors with different speeds can be mixed in a system, given the prior rules are

met. If this condition is detected, all processor speeds are set to the lowest common

denominator (highest common speed) and an error is reported.

Processor stepping within a common processor family can be mixed as long as it is

listed in the processor specification updates published by Intel Corporation.

Loading...

Loading...