8-18 Status Structure

Event enable registers

As Figure 8-1 shows, each status register set has an enable register. Each event register bit is

logically ANDed (&) to a corresponding enable bit of an enable register. Therefore, when an

e

vent bit is set and the corresponding enable bit is set (as programmed by the user), the output

(summary) of the register will set to 1, which in turn sets the summary bit of the status byte

register.

The commands to program and read the event enable registers are listed in T

able 8-5. For

details on programming and reading registers, see “Programming enable registers” and

“Reading registers” on page 8-5.

NOTE The bits of any

enable register can be reset to 0 by sending the 0 parameter value with

the appropriate enable command (i.e. STATus:OPERation:ENABle 0).

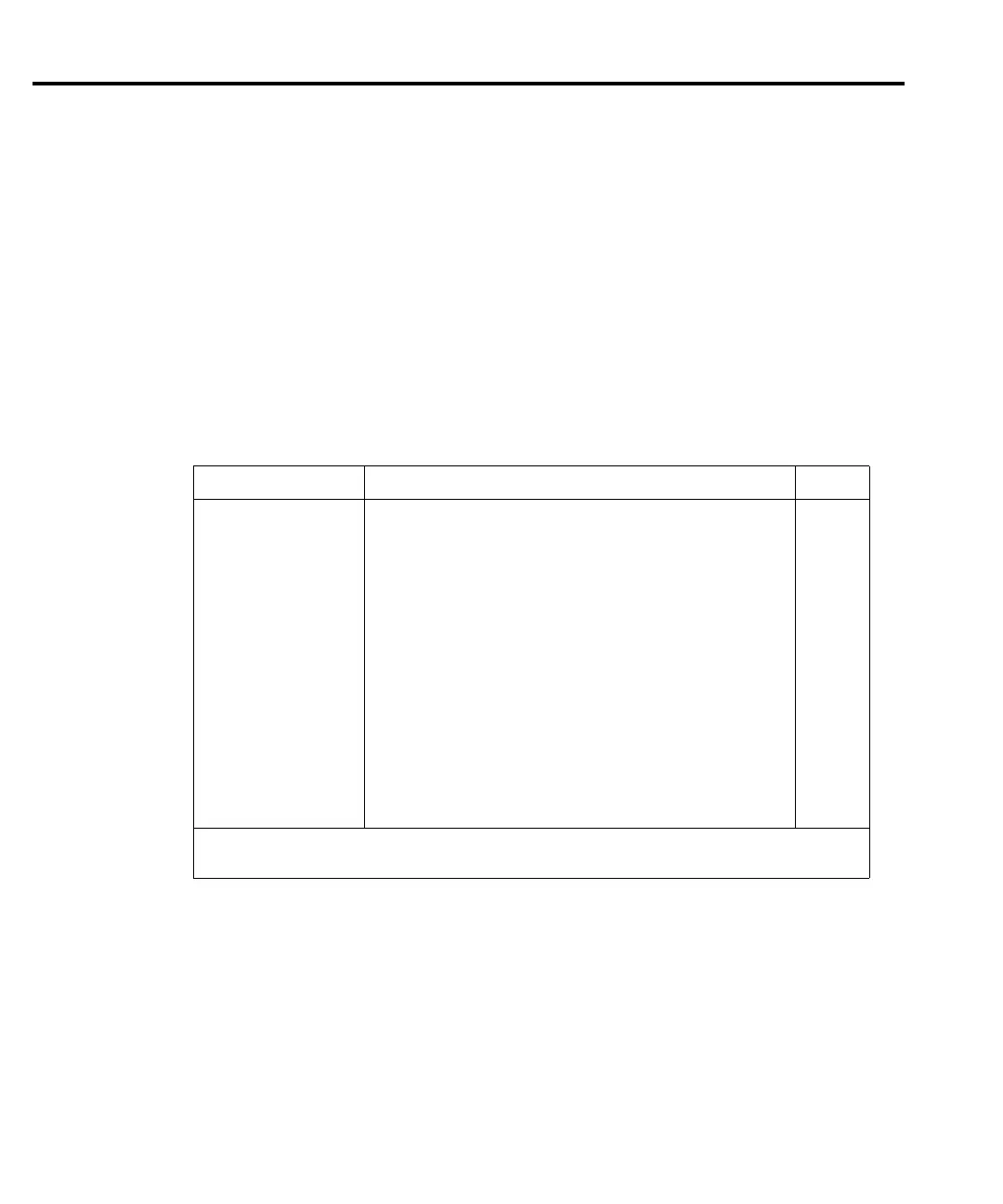

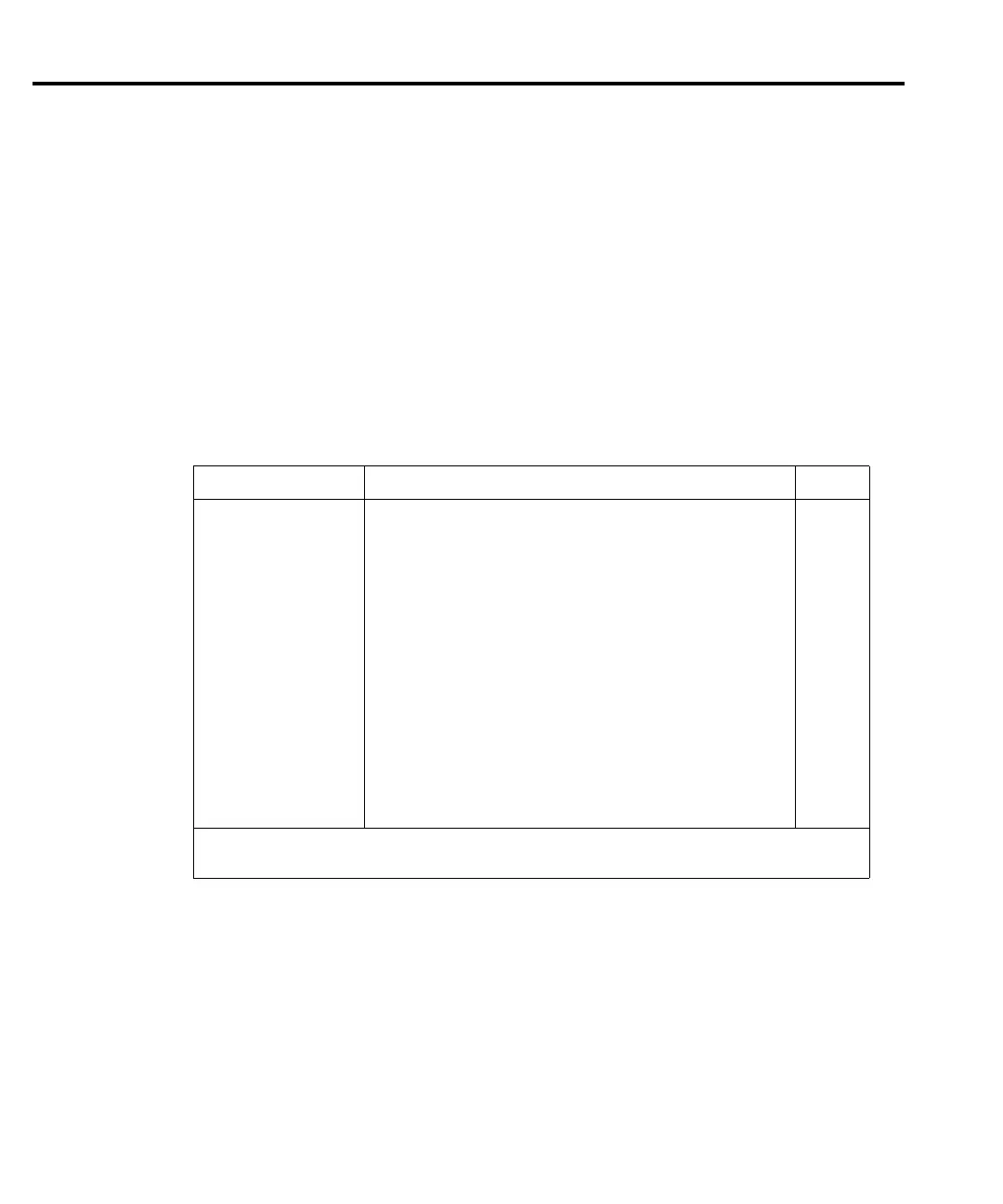

Table 8-5

Common and SCPI commands — event enable registers

Command Description Default

*ESE <NRf>

*ESE?

STATus

:OPERation

:ENABle <NRf>

:ENABle?

:MEASurement

:ENABle <NRf>

:ENABle?

:QUEStionable

:ENABle <NRf>

:ENABle?

Program standard event enable register (see “Parameters”).

Read standard event enable register.

STATus subsystem:

Operation event enable register:

Program enable register (see “Pa

rameters”).

Read enable register.

Measurement event enable register:

Program enable register (see “Pa

rameters”).

Read enable register.

Questionable event enable register:

Program enable register (see “Pa

rameters”).

Read enable register:

(Note)

Parameters:

<NRf> = 0 to 65535 Decimal format

Note: Power-up and STATus:PRESet resets all bits of all enable registers to 0. *CLS has no effect.

STATus:PRESet has no effect on settings for *ESE.

Test Equipment Depot - 800.517.8431 - 99 Washington Street Melrose, MA 02176

TestEquipmentDepot.com

Loading...

Loading...