© National Instruments | 5-3

cDAQ-9185/9189 User Manual

DI Sample Clock Signal

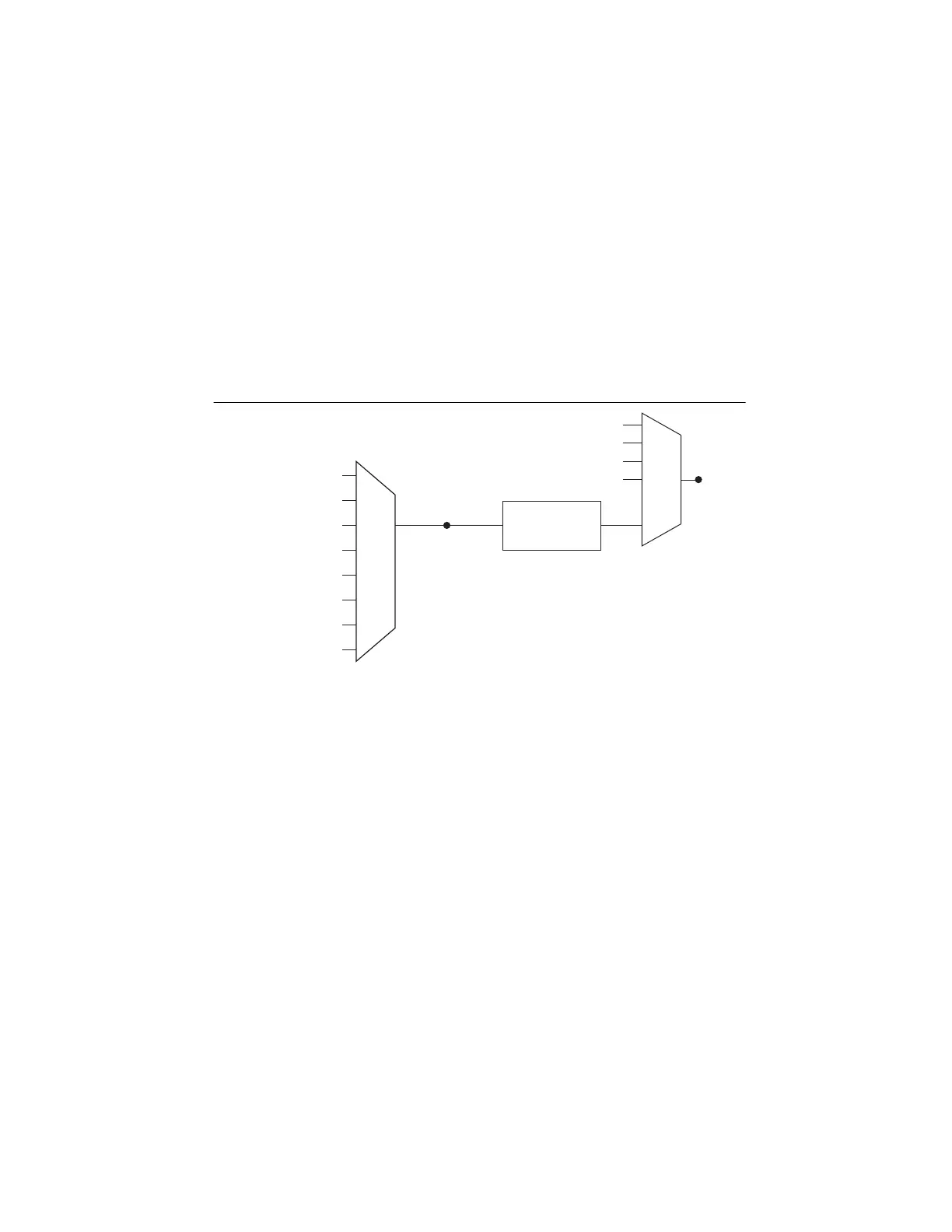

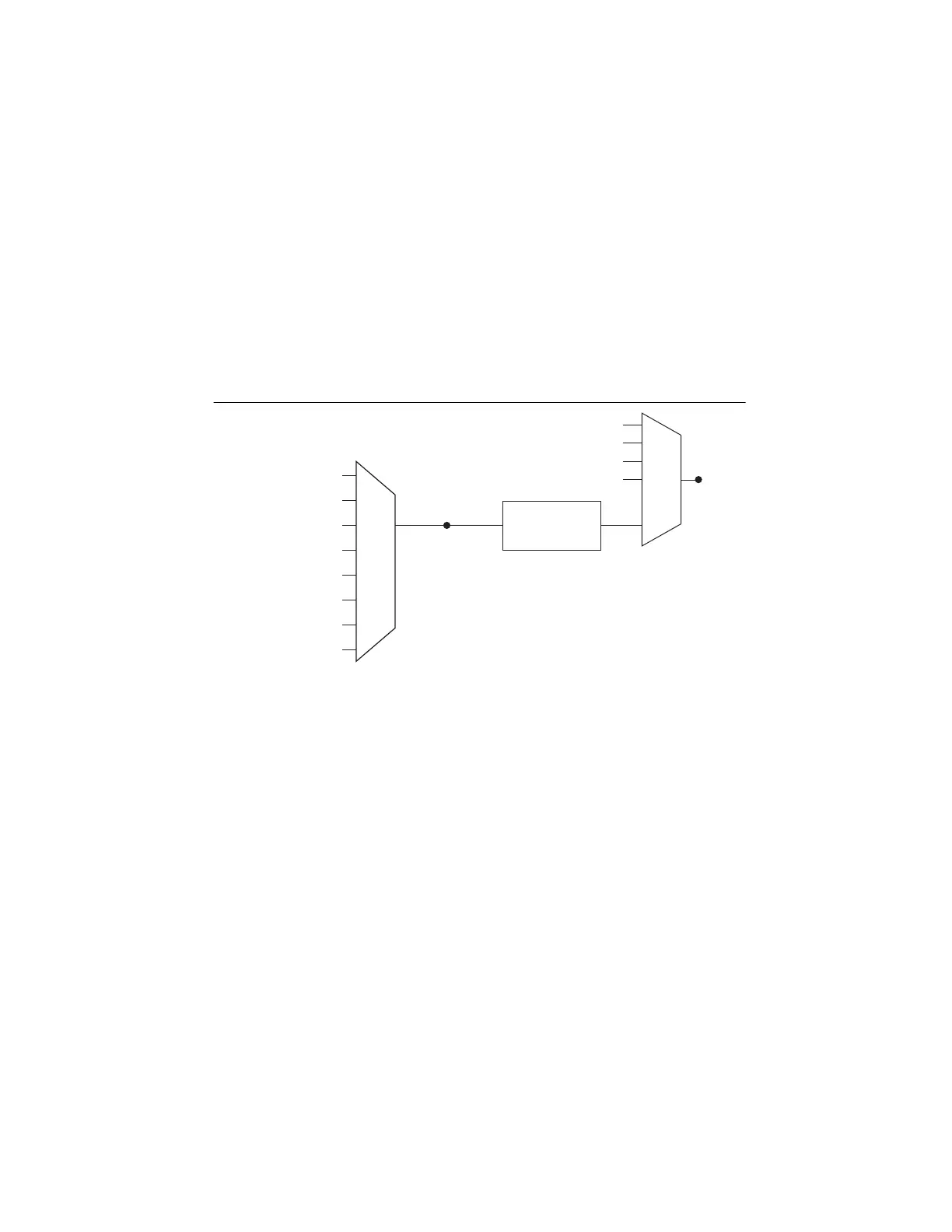

Use the DI Sample Clock (di/SampleClock) signal to sample digital I/O on any slot using

parallel digital modules, and store the result in the DI waveform acquisition FIFO. If the cDAQ

chassis receives a DI Sample Clock signal when the FIFO is full, it reports an overflow error to

the host software.

A sample consists of one reading from each channel in the DI task. DI Sample Clock signals the

start of a sample of all digital input channels in the task. DI Sample Clock can be generated from

external or internal sources as shown in Figure 5-1.

Figure 5-1. DI Sample Clock Timing Options

Routing DI Sample Clock to an Output Terminal

You can route DI Sample Clock to any output PFI terminal.

DI Sample Clock Timebase Signal

The DI Sample Clock Timebase (di/SampleClockTimebase) signal is divided down to provide

a source for DI Sample Clock. DI Sample Clock Timebase can be generated from external or

internal sources. DI Sample Clock Timebase is not available as an output from the chassis.

Using an Internal Source

To use DI Sample Clock with an internal source, specify the signal source and the polarity of the

signal. Use the following signals as the source:

• AI Sample Clock

• AO Sample Clock

• Counter n Internal Output

• Frequency Output

• DI Change Detection Output

Programmable

Clock

Divider

DI Sample Clock

Timebase

PFI

Analog Comparison Event

Ctr

n

Internal Output

DI Sample

Clock

Sigma-Delta Module Internal Output

Analog Comparison

Event

80 MHz Timebase

20 MHz Timebase

PFI

13.1072 MHz Timebase

12.8 MHz Timebase

10 MHz Timebase

100 kHz Timebase

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...