ATA Bus Interface and ATA Commands

Quantum Fireball Plus AS 10.2/20.5/30.0/40.0/60.0 GB AT 6-9

Note:

Note:Note:

Note:

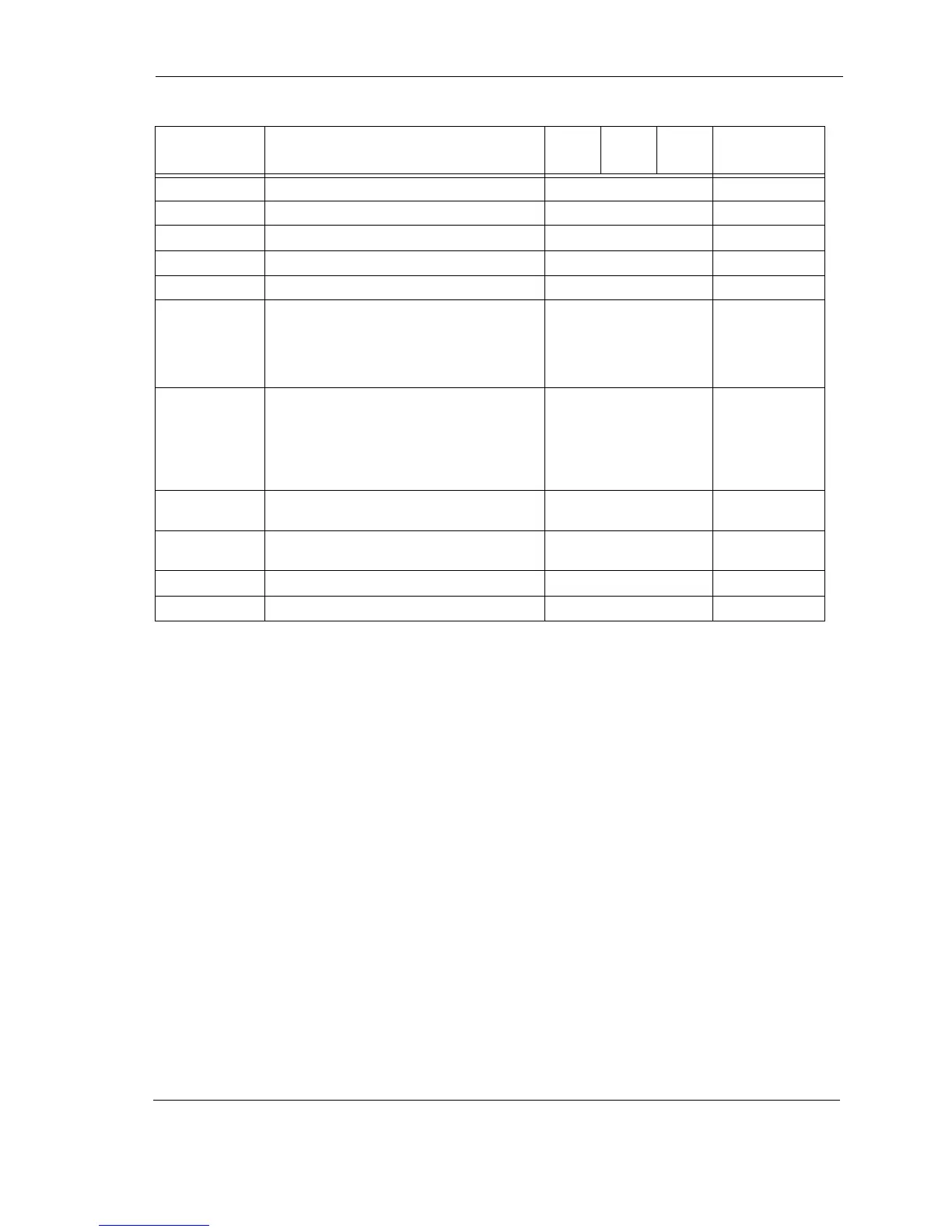

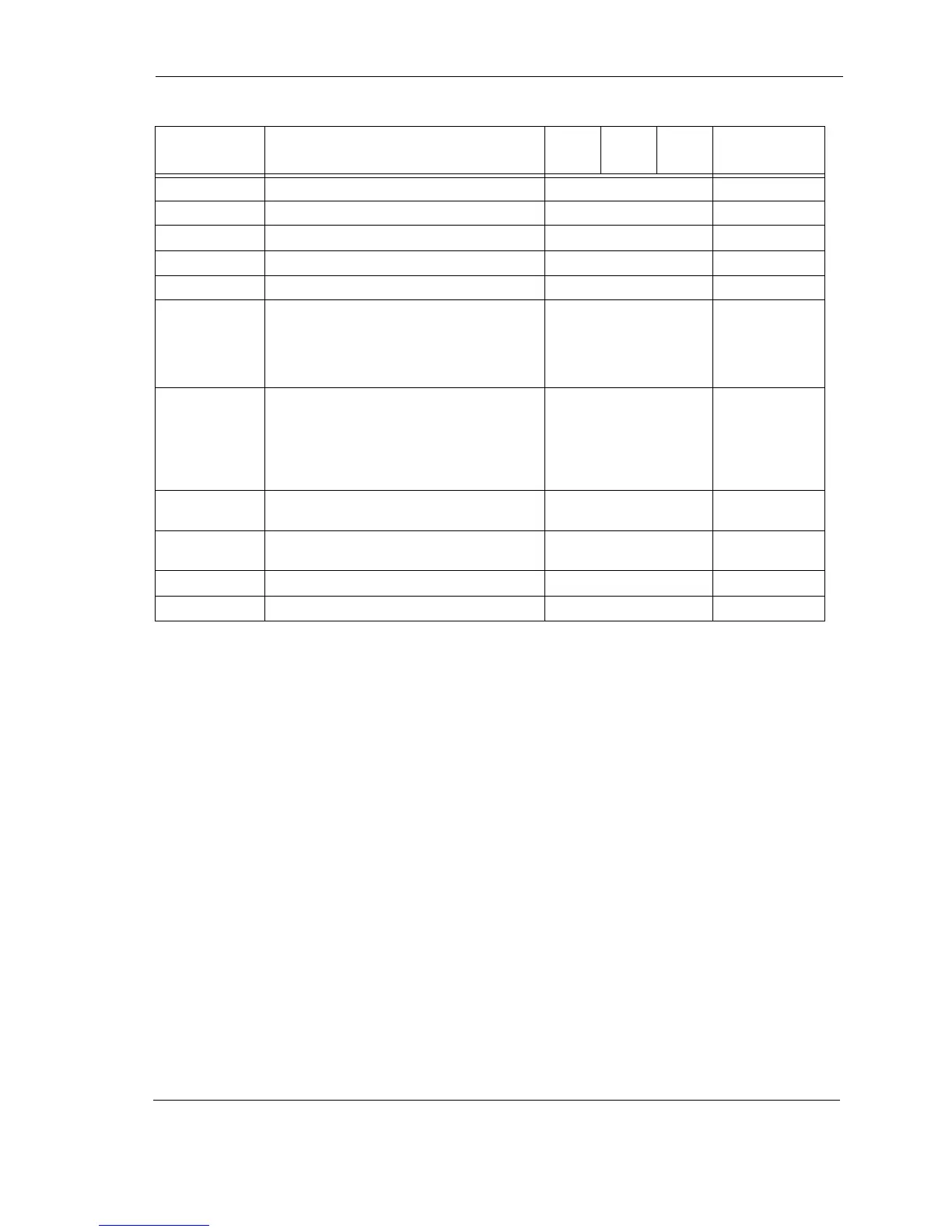

1. See signal descriptions for information on source of these signals.

2. Used during Ultra DMA protocol only.

3. Pins numbered 2, 19, 22, 24, 26, 30, and 40 are ground.

4. Pin number 20 is the Key Pin.

5. CBLID– during device based cable detection on devices supporting Ultra

DMA modes higher than 2.

6.4.2

6.4.26.4.2

6.4.2 Host Interface Timing

Host Interface TimingHost Interface Timing

Host Interface Timing

6.4.2.1

6.4.2.16.4.2.1

6.4.2.1 Programmed I/O (PIO) Transfer Mode

Programmed I/O (PIO) Transfer ModeProgrammed I/O (PIO) Transfer Mode

Programmed I/O (PIO) Transfer Mode

The PIO host interface timing shown in Table 6-5 is in reference to signals at 0.8

volts and 2.0 volts. All times are in nanoseconds, unless otherwise noted. Figure 6-

1 provides a timing diagram.

33 DEVICE ADDRESS BIT 1 —> DA1

36 DEVICE ADDRESS BIT 2 —> DA2

29 DMA ACKNOWLEDGE —> DMACK–

21 DMA REQUEST <— DMARQ

31 INTERRUPT REQUEST <— INTRQ

25 I/O READ

DMA ready on data in bursts (see note

2)

Data strobe on data out bursts (see

note 2)

—>

—>

—>

DIOR–

HDMARDY–

HSTROBE

27 I/O READY

DMA ready on data out bursts (see

note 2)

Data strobe on data in bursts (see note

2)

<—

<—

<—

IORDY

DDMARDY–

DSTROBE

23 I/O WRITE

STOP (see note 2)

—>

—>

DIOW–

STOP

34 PASSED DIAGNOSTCS/CABLE

DETECTION

(See Notes 1 & 5) PDIAG–/CBLID–

1 RESET —> RESET

32 I/O CS16 <— IOCS16

J1 PIN

J1 PIN J1 PIN

J1 PIN

NUMBER

NUMBERNUMBER

NUMBER

DESCRIPTION

DESCRIPTIONDESCRIPTION

DESCRIPTION HOST

HOSTHOST

HOST DIR

DIRDIR

DIR DEV

DEVDEV

DEV ACRONYM

ACRONYMACRONYM

ACRONYM

Loading...

Loading...