ATA Bus Interface and ATA Commands

6-18 Quantum Fireball Plus AS 10.2/20.5/30.0/40.0/60.0 GB AT

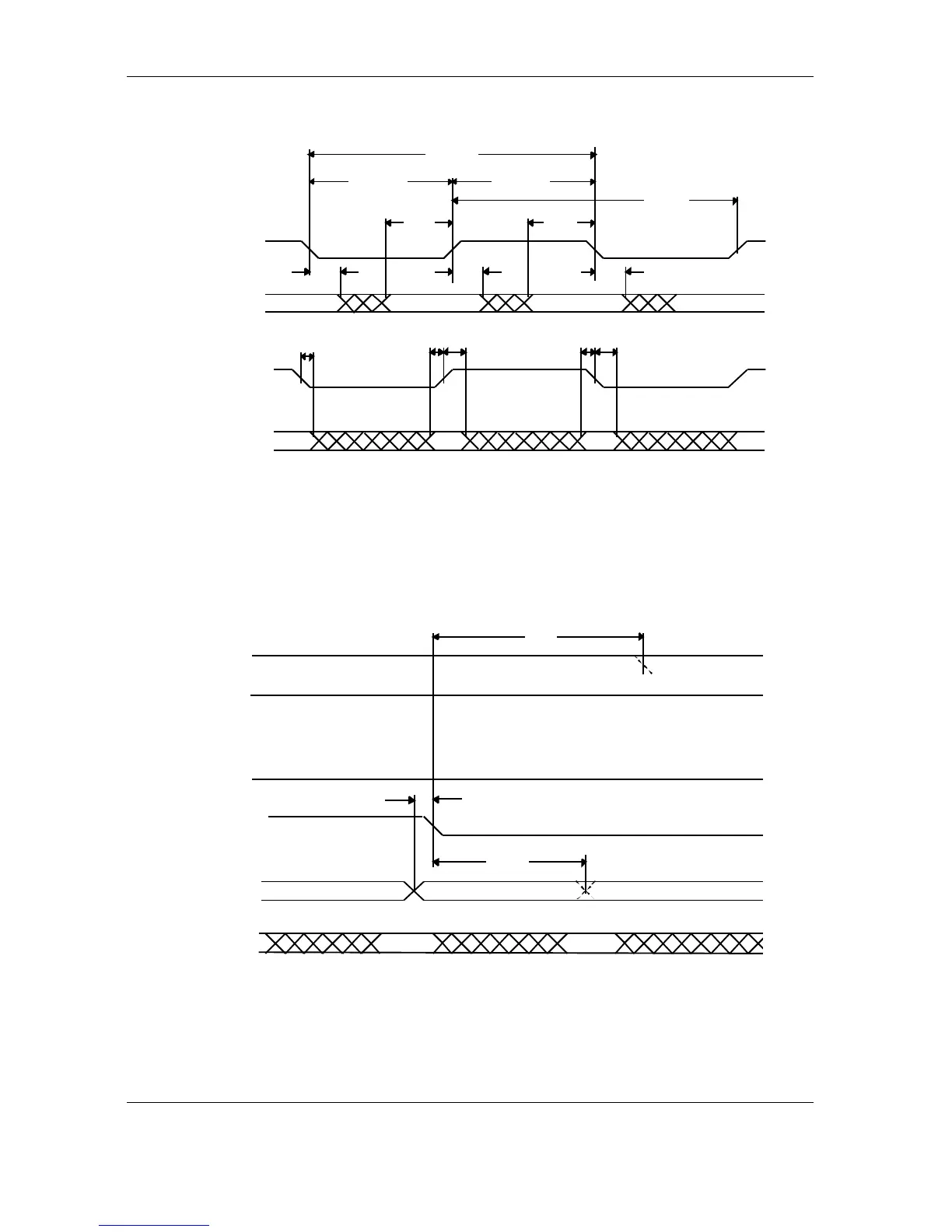

Figure 6-9

Figure 6-9 Figure 6-9

Figure 6-9 Sustained Data Out Burst

Note:

Note:Note:

Note: DD(15:0) and HSTROBE signals are shown at both the device

and the host to emphasize that cable settling time as well as

cable propagation delay shall not allow the data signals to be

considered stable at the device until well after they are driven

by the host.

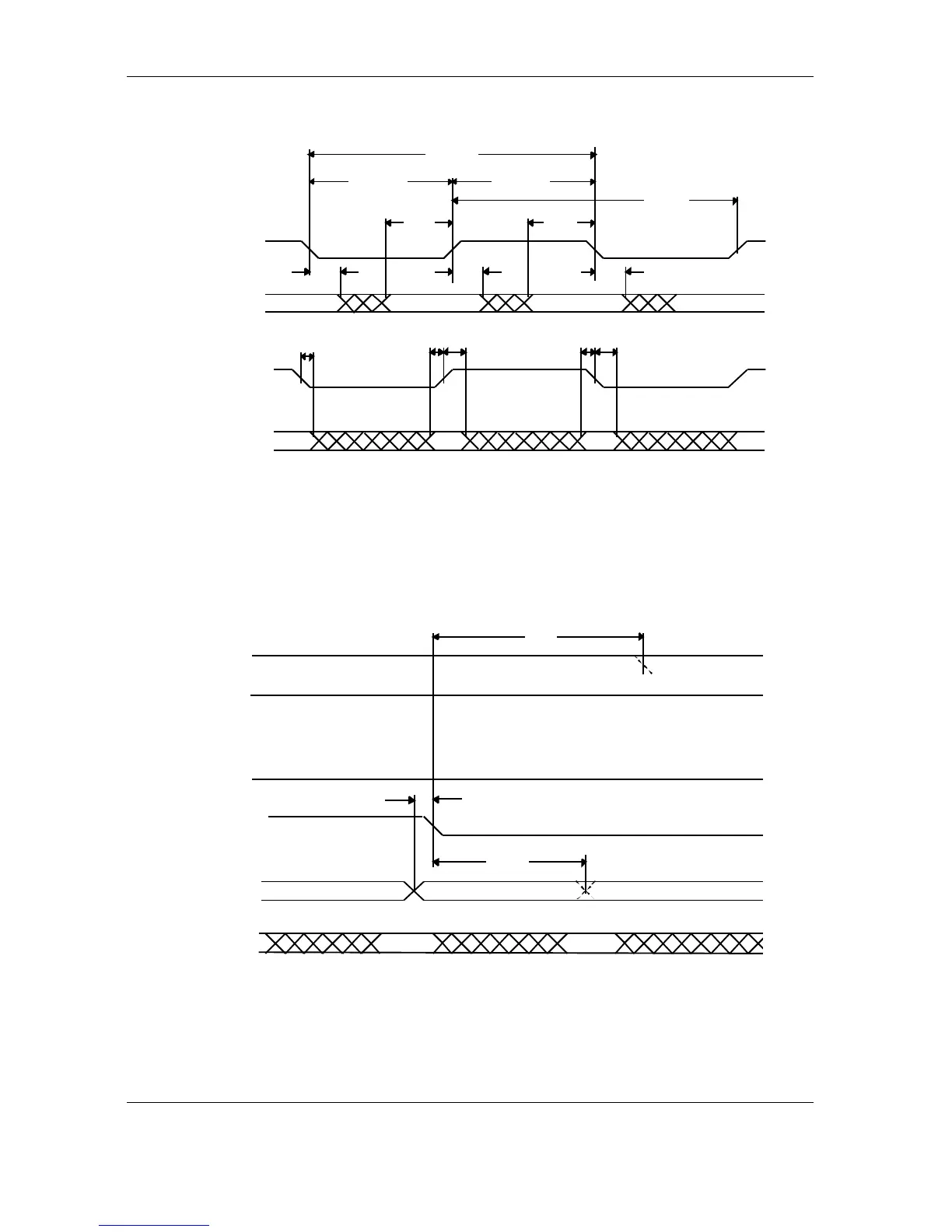

Figure 6-10

Figure 6-10 Figure 6-10

Figure 6-10

Device Pausing a Data Out Burst

Note:

Note:Note:

Note: The device knows the burst is fully paused Trp ns after

DDMARDY- is negated and may then negate DMARQ to

terminate the burst. Tsr timing need not be met for an

asynchronous pause.

Tdh

Tds

Tdvh

HSTROBE

at host

DD(15:0)

at host

HSTROBE

at device

DD(15:0)

at device

Tdvh

Tcyc Tcyc

Tdvs Tdvs

Tds Tdh

T2cyc

Tdh

Tdvh

T2cyc

DMARQ

(device)

DMACK-

(host)

STOP

(host)

DDMARDY-

(device)

HSTROBE

(host)

DD(15:0)

(host)

Tsr

Trfs

Trp

Loading...

Loading...