Branch on Condition

(BCR)

(BC)

General

Description

Format

(II)

(RX)

Condition

Code

Interrupt Action

Notes

Branching Instructions

•

If

the

condition code is set to

any

of

the

conditions specified by

the

four-bit mask field (M

or

M

1

),

the P counter is replaced by

the

branch

address (R

2

or

X

2

/B

2

/D

2

).

If

the

four-bit mask field

(M

or

Md

is not

equivalent to the condition code settings, branching does

not

occur

and

the

next instruction in sequence is executed. The branch is initiated when-

ever

the

condition code has a corresponding mask

bit

set.

0

0

•

•

•

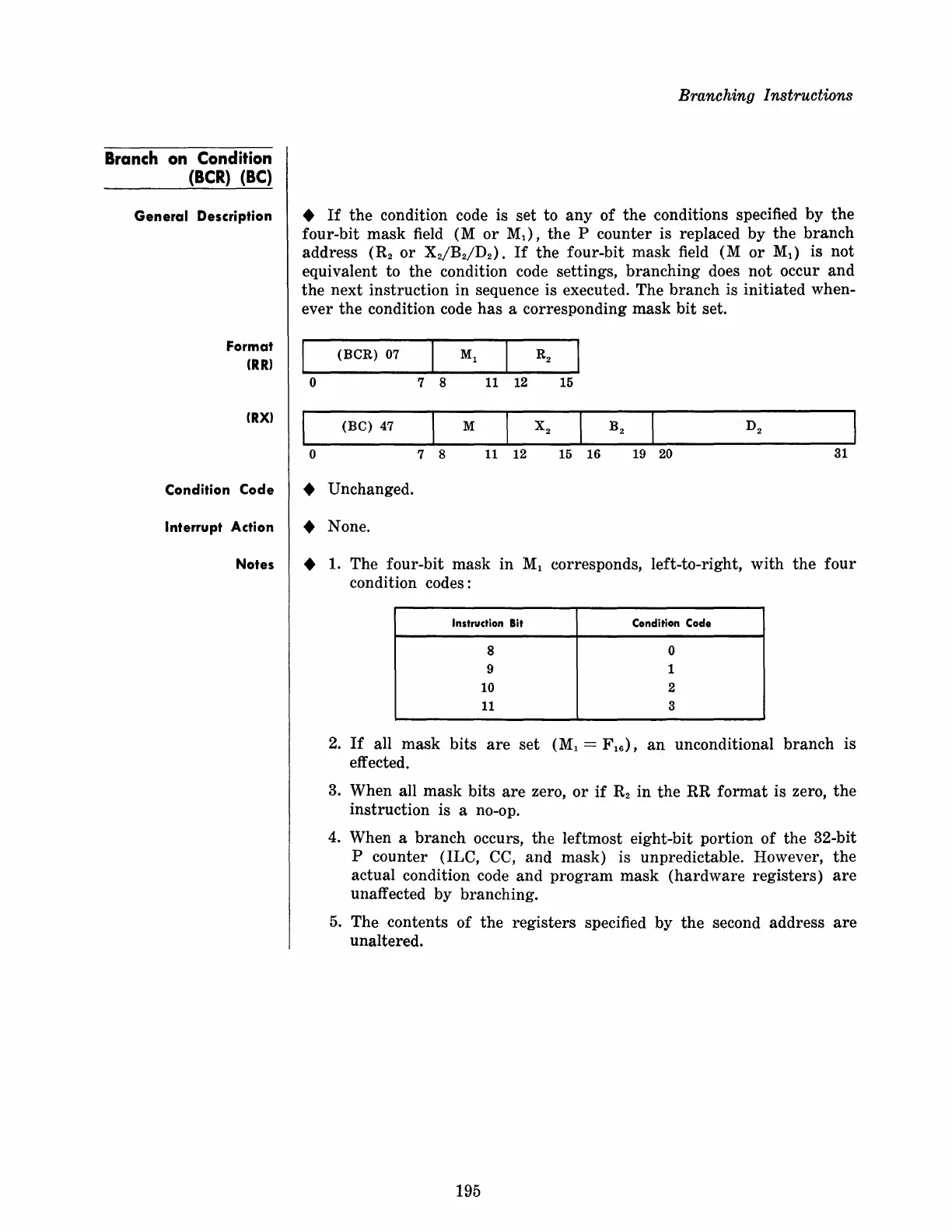

(BCR)

07

Ml

R2

7 8

11

12 15

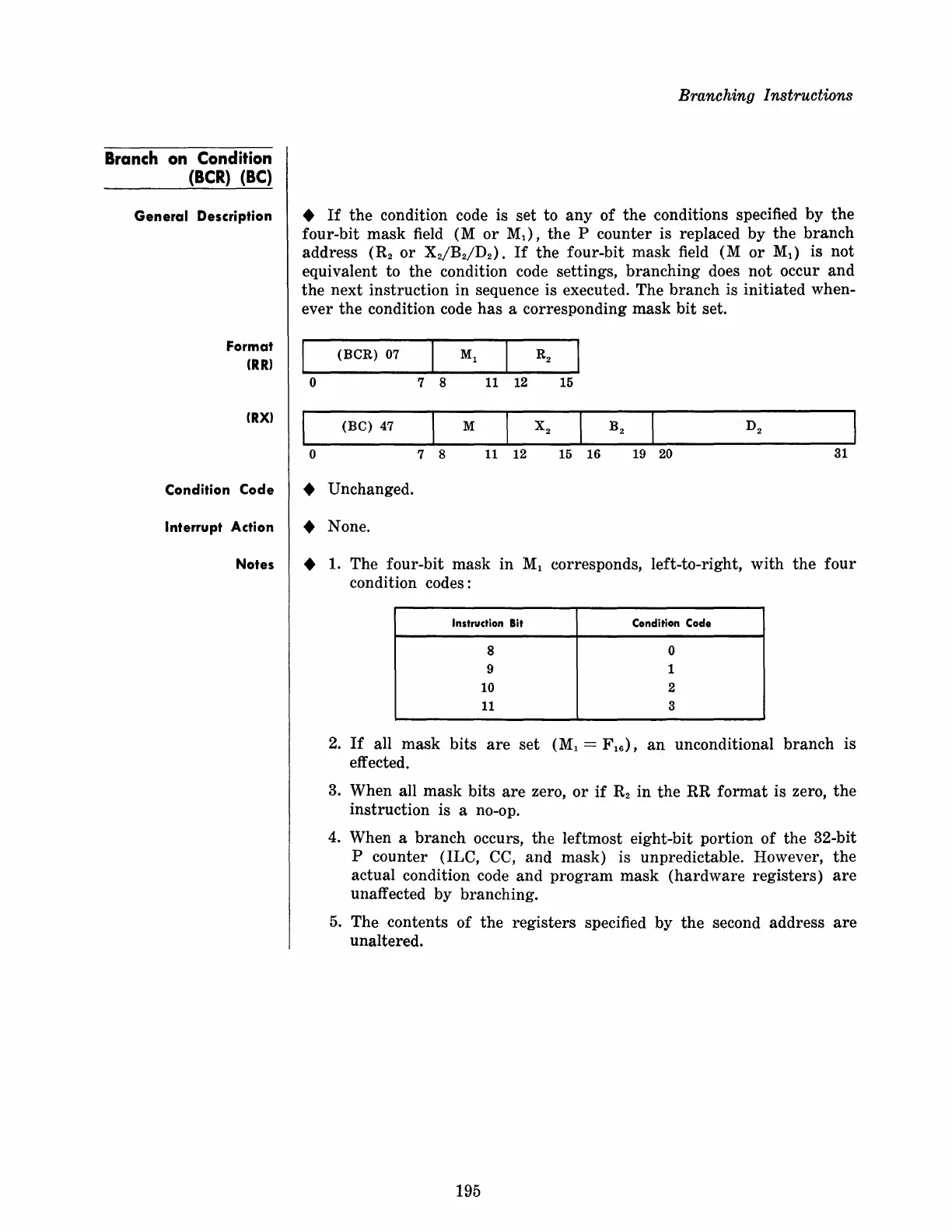

(BC)

47

M

X

2

B2

D2

7

8

11

12

15

16

19

20

31

Unchanged.

None.

1.

The four-bit mask in

Ml

corresponds, left-to-right, with

the

four

condition codes:

Instruction Bit Condition Code

8 0

9 1

10

2

11

3

2.

If

all mask bits

are

set

(M

1

= F

1G

),

an

unconditional branch is

effected.

3.

When all mask bits

are

zero,

or

if

R2

in

the

RR

format

is zero,

the

instruction is a

nO-OPe

4.

When a

branch

occurs, the leftmost eight-bit portion

of

the

32-bit

P counter (ILC,

CC,

and mask) is unpredictable. However,

the

actual condition code and

program

mask

(hardware

registers)

are

unaffected by branching.

5.

The contents of the registers specified by

the

second address

are

unaltered.

195

Loading...

Loading...