Branch on Count

(BCTR)

(BCT)

General Description

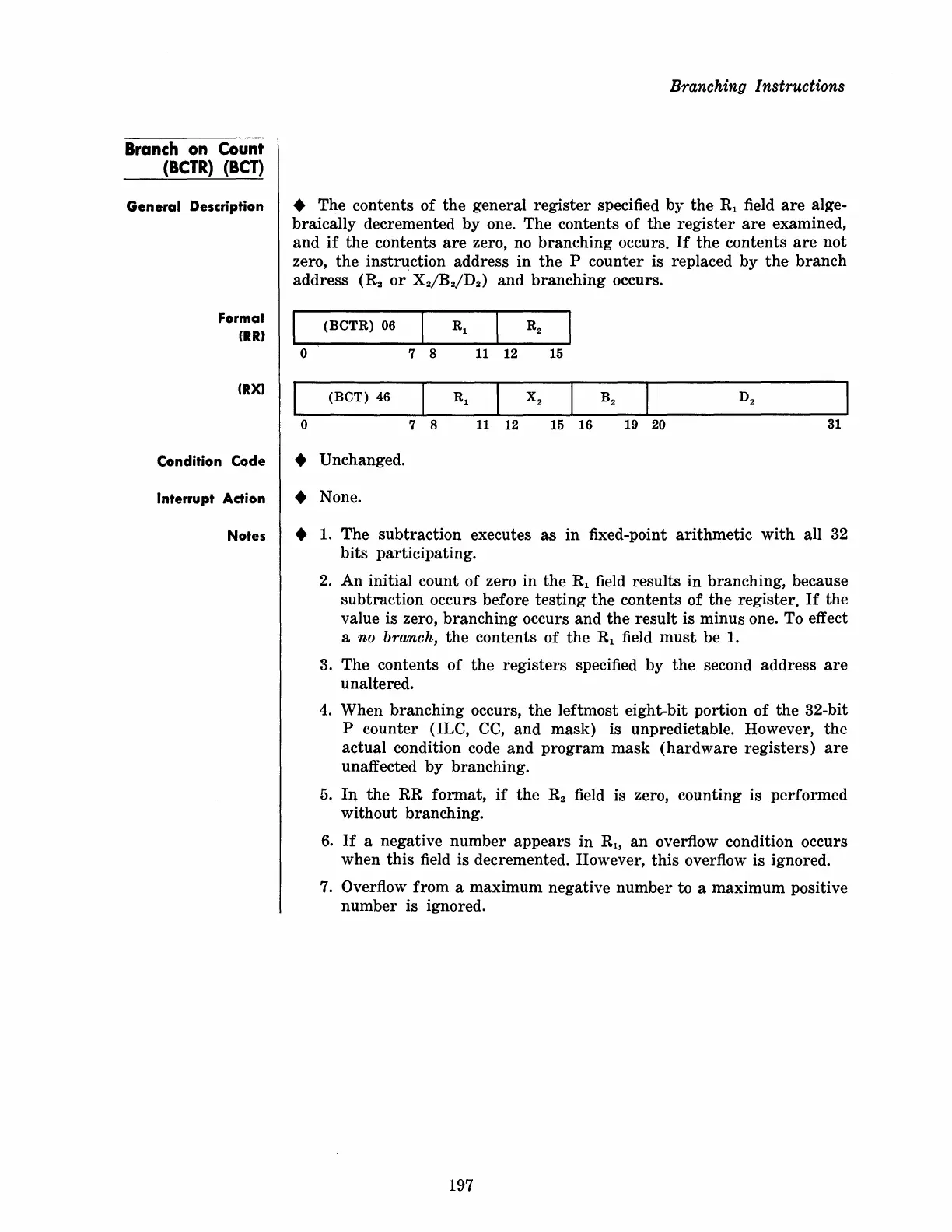

Format

(RR)

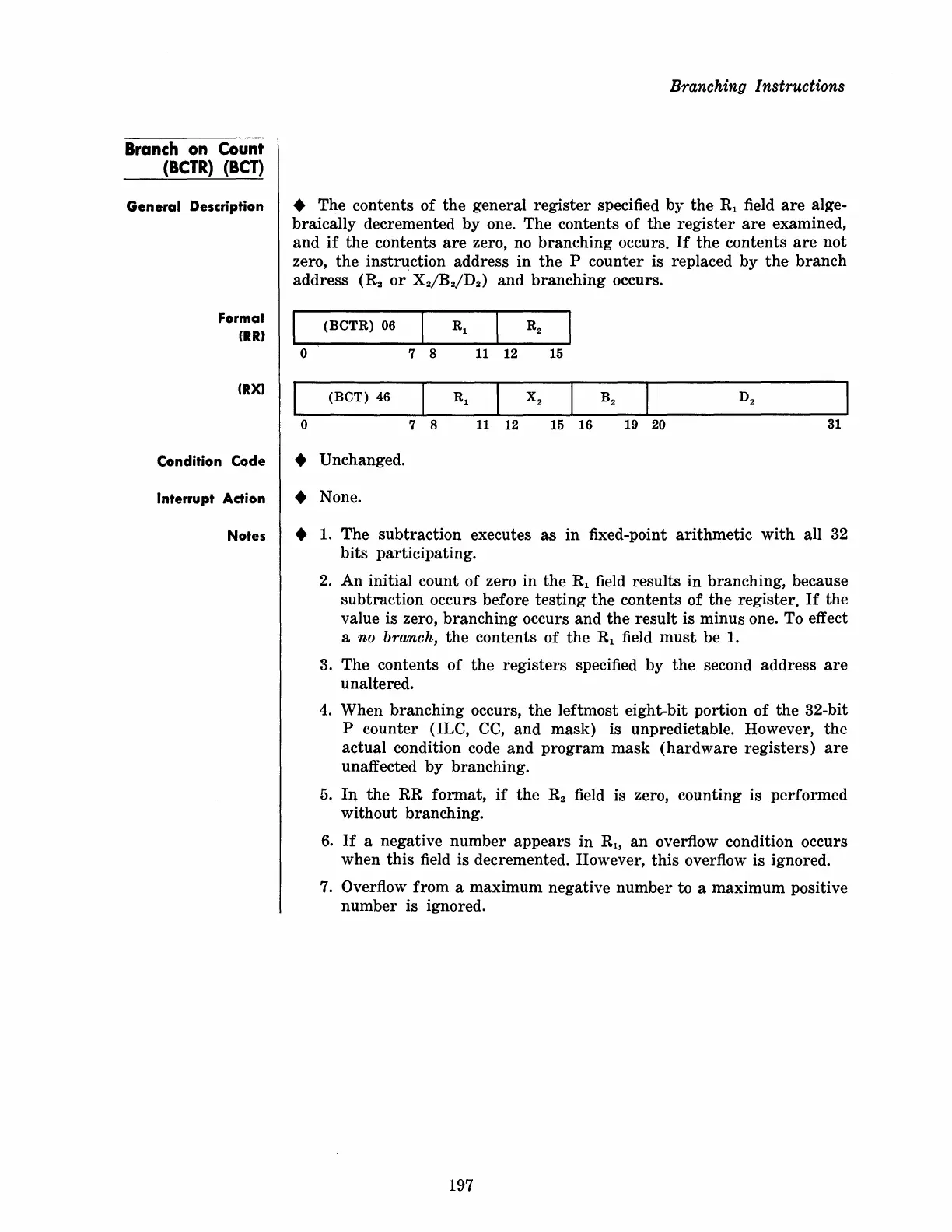

(RX)

Condition Code

Interrupt Action

Notes

Branching Instructions

• The contents of

the

general

register

specified by

the

Rl field

are

alge-

braically decremented by one. The contents

of

the

register

are

examined,

and

if

the contents

are

zero, no branching occurs.

If

the

contents

are

not

zero,

the

instruction address in

the

P counter is replaced by

the

branch

address

(~

or

X

2

/B

2

/D

2

)

and

branching occurs.

(BCTR)

06

Rl

R2

0

7

8 11

12

15

(BCT)

46

Rl

X

2

B2

D2

0

7 8 11

12 15

16

19

20

31

•

Unchanged.

•

None.

• 1. The subtraction executes

as

in

fixed-point arithmetic

with

all 32

bits participating.

2.

An initial count of zero

in

the

Rl field results in branching, because

subtraction occurs before testing

the

contents

of

the

register.

If

the

value is zero, branching occurs

and

the

result is minus one. To effect

a

no branch,

the

contents of

the

Rl field

must

be 1.

3. The contents

of

the

registers specified by

the

second address

are

unaltered.

4.

When branching occurs,

the

leftmost eight-bit portion

of

the 32-bit

P counter

OLe,

ee,

and

mask) is unpredictable. However,

the

actual condition code and

program

mask

(hardware

registers)

are

unaffected by branching.

5.

In

the

RR format,

if

the

R2

field is zero, counting is performed

without branching.

6.

If

a negative number appears in R

1

,

an

overflow condition occurs

when

this

field is decremented. However, this overflow is ignored.

7. Overflow from a maximum negative number to a maximum positive

number is ignored.

197

Loading...

Loading...