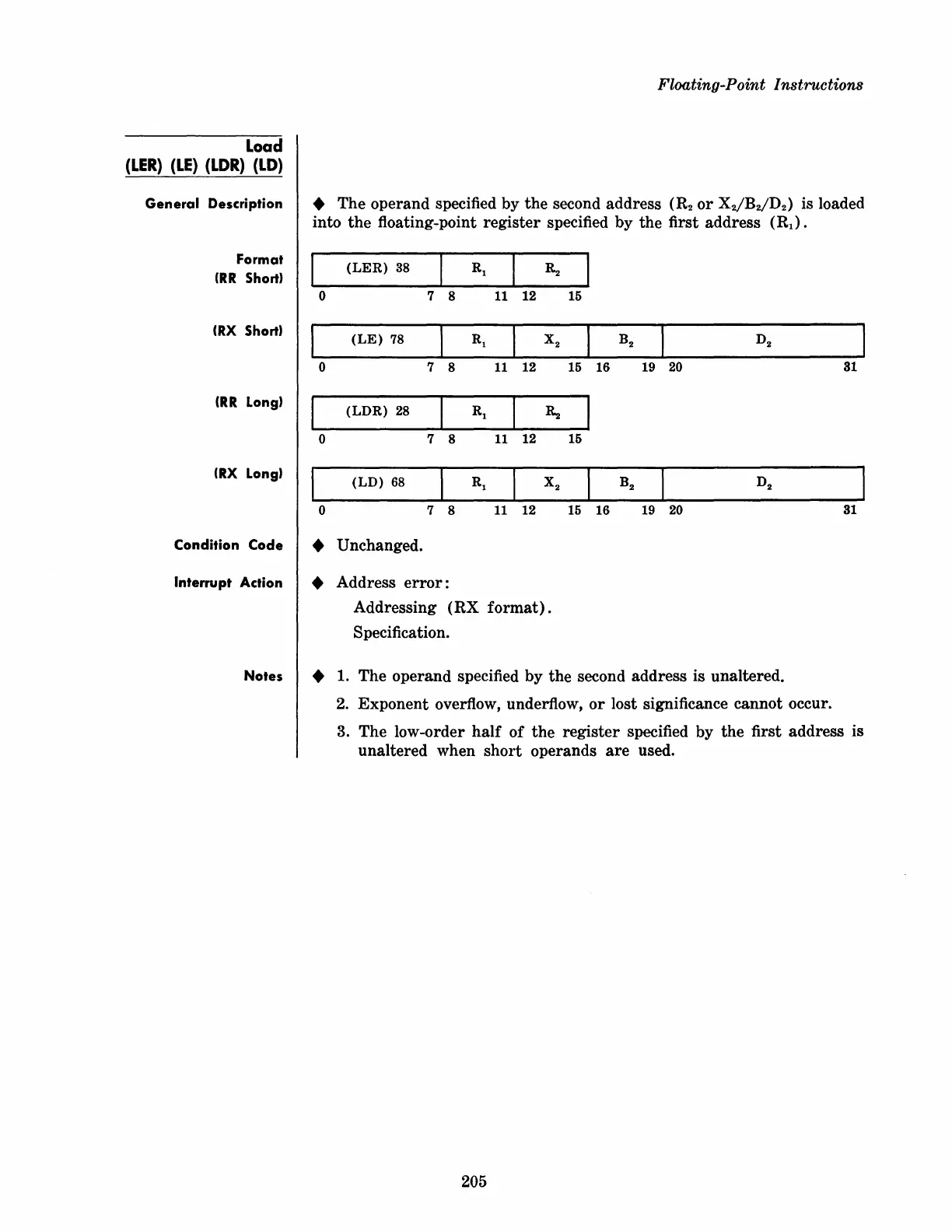

Floating-Point Instructions

Load

(LER)

(LE)

(LDR)

(LD)

General Description

• The operand specified by

the

second address

(R

2

or

X~B~D2)

is loaded

into

the

floating-point

register

specified

by

the first address

(R

1

).

Format

(LER)

38

Rl

R2

(RR

Short)

0 7 8

11

12

15

(RX Short)

(LE)

78

Rl

X

2

B2

D2

0 7

8

11

12

15

16

19

20

31

(RR

Long)

(LDR)

28

Rl

~

0 7 8 11

12

15

(RX Long)

(LD)

68

Rl

X

2

B2

D2

0 7 8

11

12

15

16

19

20

31

Condition Code

•

Unchanged.

Interrupt Action

•

Address

error:

Addressing

(RX

format).

Specification.

Notes • 1. The operand specified

by

the second address is unaltered.

2.

Exponent overflow, underflow,

or

lost significance cannot occur.

3. The low-order

half

of

the

register

specified

by

the

first address is

unaltered when

short

operands

are

used.

205

Loading...

Loading...