PRIVILEGED

INSTRUCTIONS

INTRODUCTION

INSTRUCTION

FORMATS

RII

Format

De~wription

De~wription

SS

Format

• The instructions described in this section

are

called privileged instruc-

tions

and can only be executed

if

the

non-privileged mode

bit

(bit

position

15 in the

Interrupt

Status

register)

for

the

current

state

is zero.

In

addition to

the

standard

privileged instruction set, inclusion

of

the

memory protect

and/or

the

direct control optional features cause additional

privileged instructions to be added.

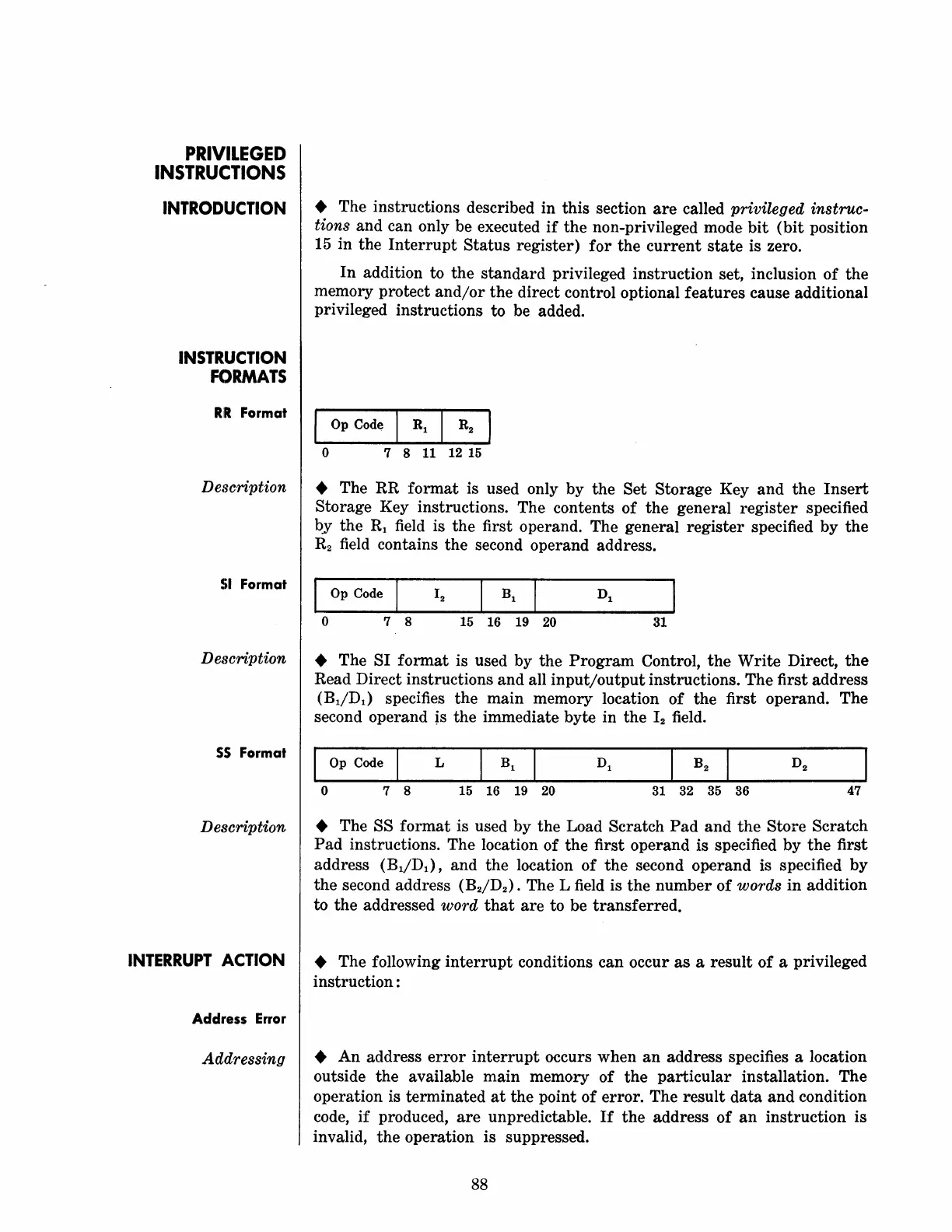

Op Code

o 7 8 11 12 15

• The RR format is used only by the

Set

Storage Key and the

Insert

Storage Key instructions. The contents

of

the

general

register

specified

by the Rl field is the first operand. The general register specified by

the

R2

field

contains the second operand address.

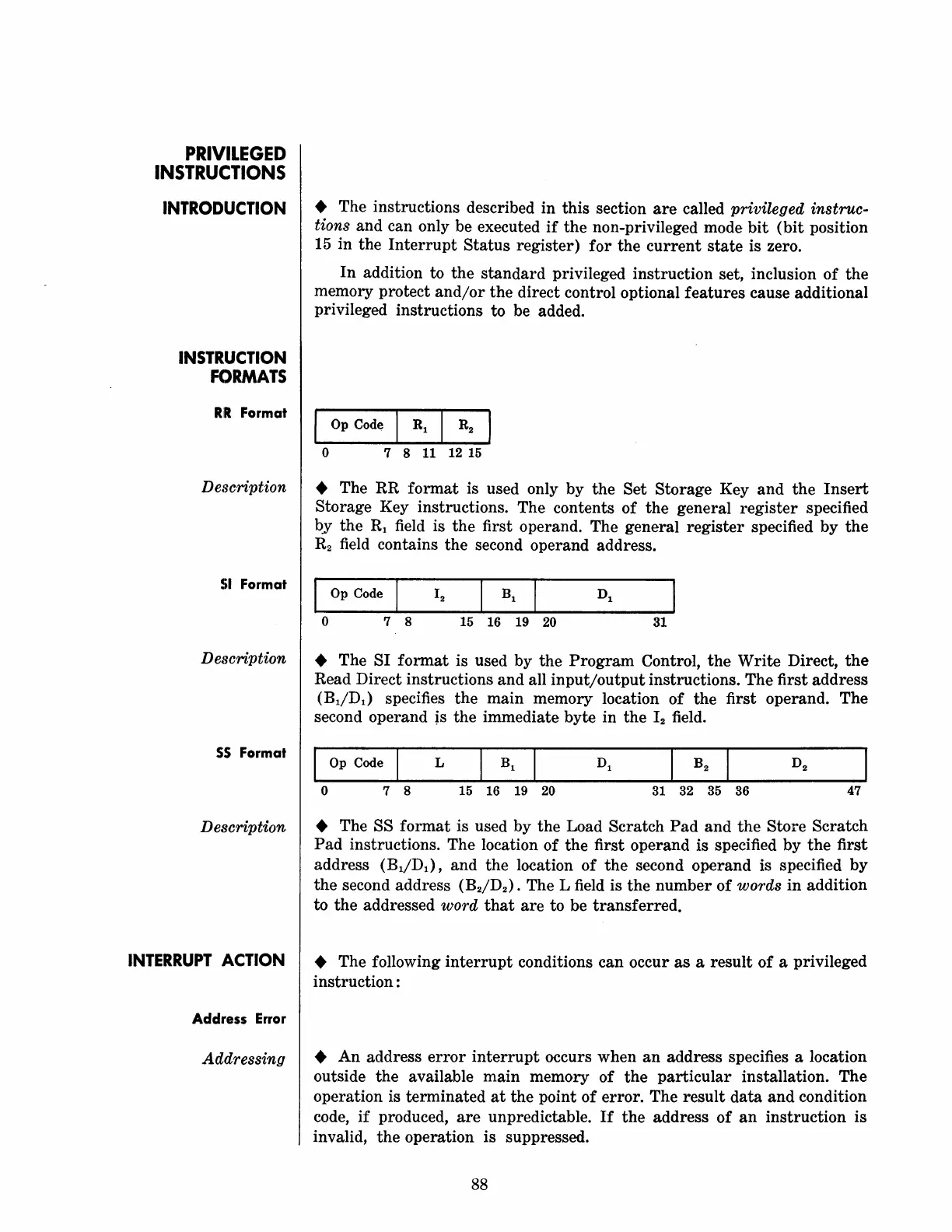

o 7 8 15 16 19

20

31

• The SI

format

is used by the

Program

Control,

the

Write

Direct,

the

Read Direct instructions and all

input/output

instructions. The first address

(BdD

1

)

specifies the main memory location

of

the first operand. The

second operand

js the immediate byte in

the

12

field.

I Op Code I L

Bl

o 7 8 15 16 19

20

31

32 35 36

47

Description • The SS format is used by the Load Scratch

Pad

and

the

Store Scratch

Pad

instructions. The location of the first operand is specified by

the

first

address (B1/D

1

),

and the location

of

the

second operand is specified by

the

second address (B

2

/D

2

).

The L field is the number

of

words in addition

to the addressed

w'ord

that

are

to be

transferred.

INTERRUPT

ACTION

• The following

interrupt

conditions can occur

as

a result

of

a privileged

instruction:

Address

Error

Addressing

• An address

error

interrupt

occurs when

an

address specifies a location

outside

the

available main memory

of

the

particular

installation. The

operation is terminated

at

the

point

of

error. The result

data

and

condition

code,

if

produced,

are

unpredictable.

If

the

address

of

an

instruction is

invalid,

the

operation

is

suppressed.

88

Loading...

Loading...