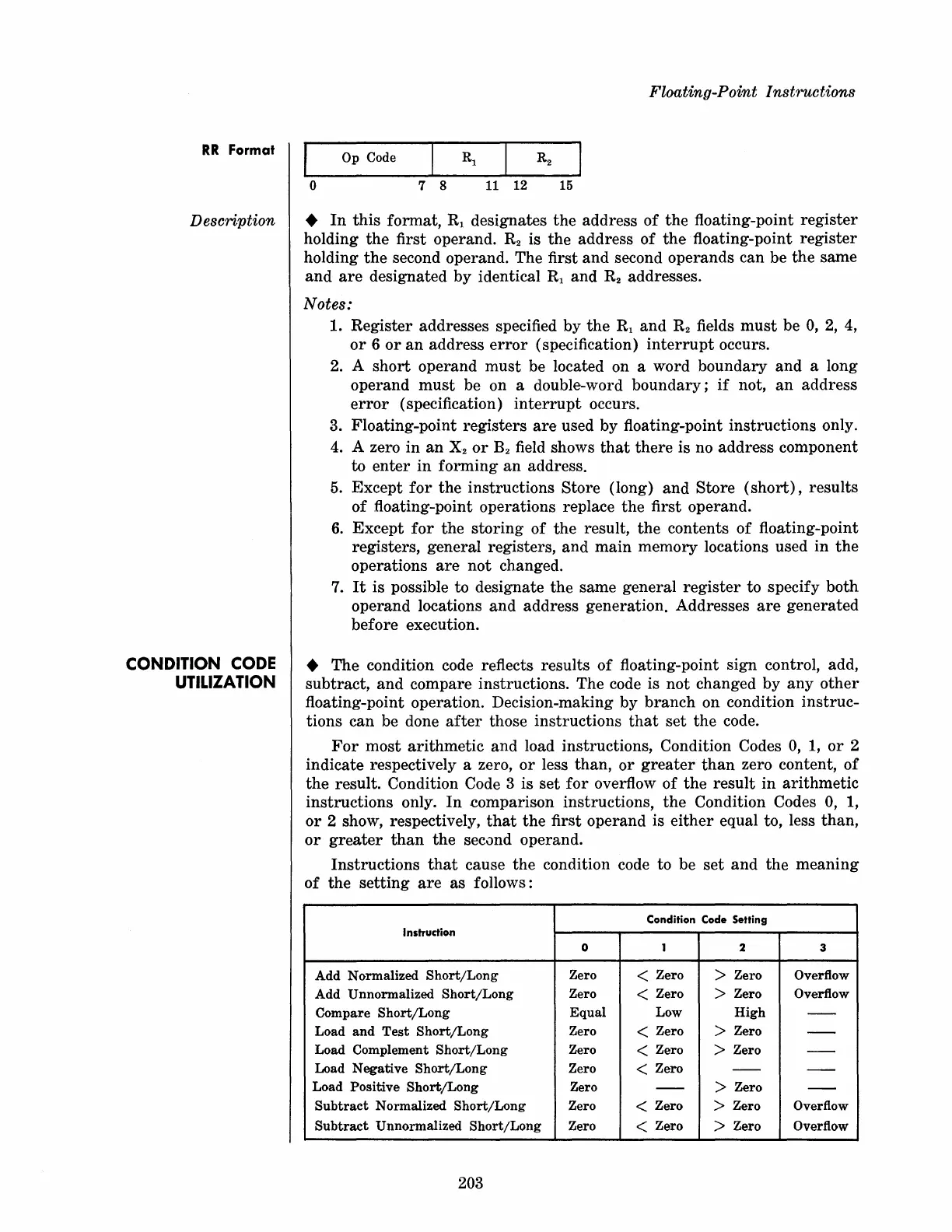

RR

Format

Description

CONDITION

CODE

UTILIZATION

Floating-Point Instructions

o

7 8 11 12 15

•

In

this

format, Rl designates

the

address

of

the

floating-point

register

holding

the

first operand.

R2

is

the

address

of

the

floating-point

register

holding

the

second operand. The first

and

second operands can be

the

same

and

are

designated

by

identical Rl

and

R2

addresses.

Notes:

1.

Register

addresses specified

by

the

Rl

and

R2

fields

must

be

0,

2, 4,

or

6

or

an

address

error

(specification)

interrupt

occurs.

2. A

short

operand

must

be located on a word

boundary

and

a long

operand

must

be on a double-word

boundary;

if

not,

an

address

error

(specification)

interrupt

occurs.

3. Floating-point

registers

are

used

by

floating-point instructions only.

4. A zero

in

an

X

2

or

B2

field shows

that

there

is no

address

component

to

enter

in

forming

an

address.

5.

Except

for

the

instructions

Store

(long)

and

Store

(short),

results

of

floating-point operations replace

the

first operand.

6.

Except

for

the

storing

of

the

result,

the

contents

of

floating-point

registers, general registers,

and

main

memory locations used in

the

operations

are

not

changed.

7.

It

is possible to designate

the

same general

register

to specify

both

operand locations

and

address generation. Addresses

are

generated

before execution.

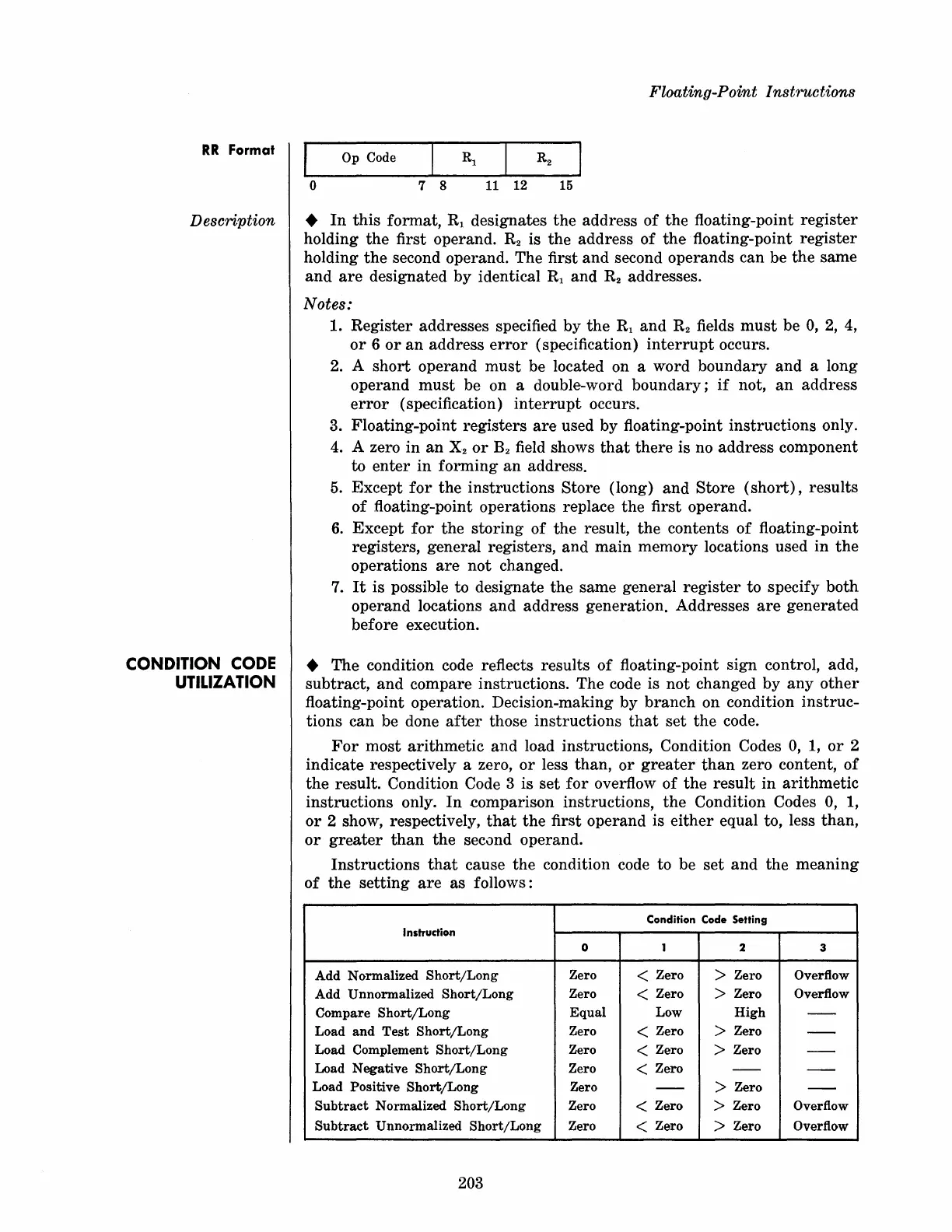

• The condition code reflects results

of

floating-point sign control, add,

subtract,

and

compare instructions. The code is

not

changed by

any

other

floating-point operation. Decision-making

by

branch

on condition

instruc-

tions can be done

after

those instructions

that

set

the

code.

For

most

arithmetic

and

load instructions, Condition Codes

0,

1,

or

2

indicate respectively a zero,

or

less

than,

or

greater

than

zero content,

of

the

result. Condition Code 3 is

set

for

overflow

of

the

result

in

arithmetic

instructions

only.

In

-comparison instructions,

the

Condition Codes 0, 1,

or

2 show, respectively,

that

the

first operand is

either

equal to, less

than,

or

greater

than

the

second operand.

Instructions

that

cause

the

condition code to be

set

and

the

meaning

of

the

setting

are

as

follows:

Condition Code Setting

Instruction

0

1 2

3

Add Normalized

Short/Long

Zero

< Zero > Zero

Overflow

Add Unnormalized

Short/Long

Zero

< Zero

> Zero

Overflow

Compare

Short/Long

Equal

Low

High

--

Load

and

Test

Short/Long

Zero

< Zero

> Zero

--

Load Complement

Short/Long

Zero

< Zero > Zero

--

Load Negative

Short/Long

Zero

< Zero

--

--

Load Positive

Short/Long

Zero

--

> Zero

--

Subtract

Normalized

Short/Long

Zero

< Zero > Zero

Overflow

Subtract

Unnormalized

Short/Long

Zero

< Zero > Zero

Overflow

203

Loading...

Loading...