DocID14024 Rev 4 11/39

UM0470 Single wire interface module (SWIM)

38

3.3 Bit format

The bit format is a return-to-zero format, which allows a synchronization of every bit. Two

communication speeds are available. At SWIM activation, the low speed is selected, while

the high speed is selected by setting the HS bit in the SWIM_CSR register with the SWIM

protocol.

When entering the SWIM mode during the RESET phase, it is possible that the option bytes

have not yet been loaded from non volatile memory to their respective registers. The option

byte loading is triggered by any internal or external reset.

In order to ensure proper system behavior, the HS bit should not be set until the option byte

loading is finished. At the end of the option byte loading, the HSIT bit in the SWIM_CSR is

set by hardware.

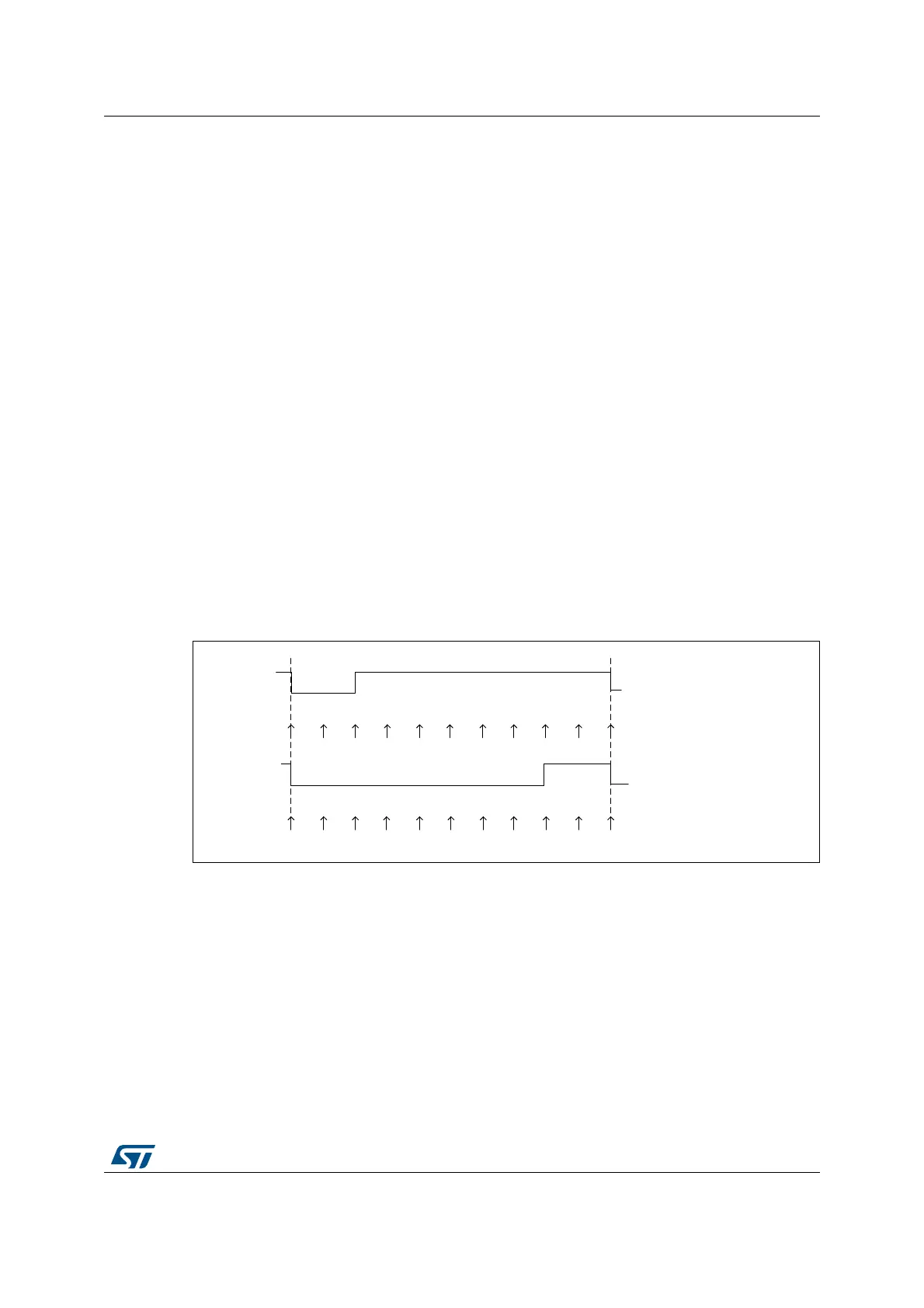

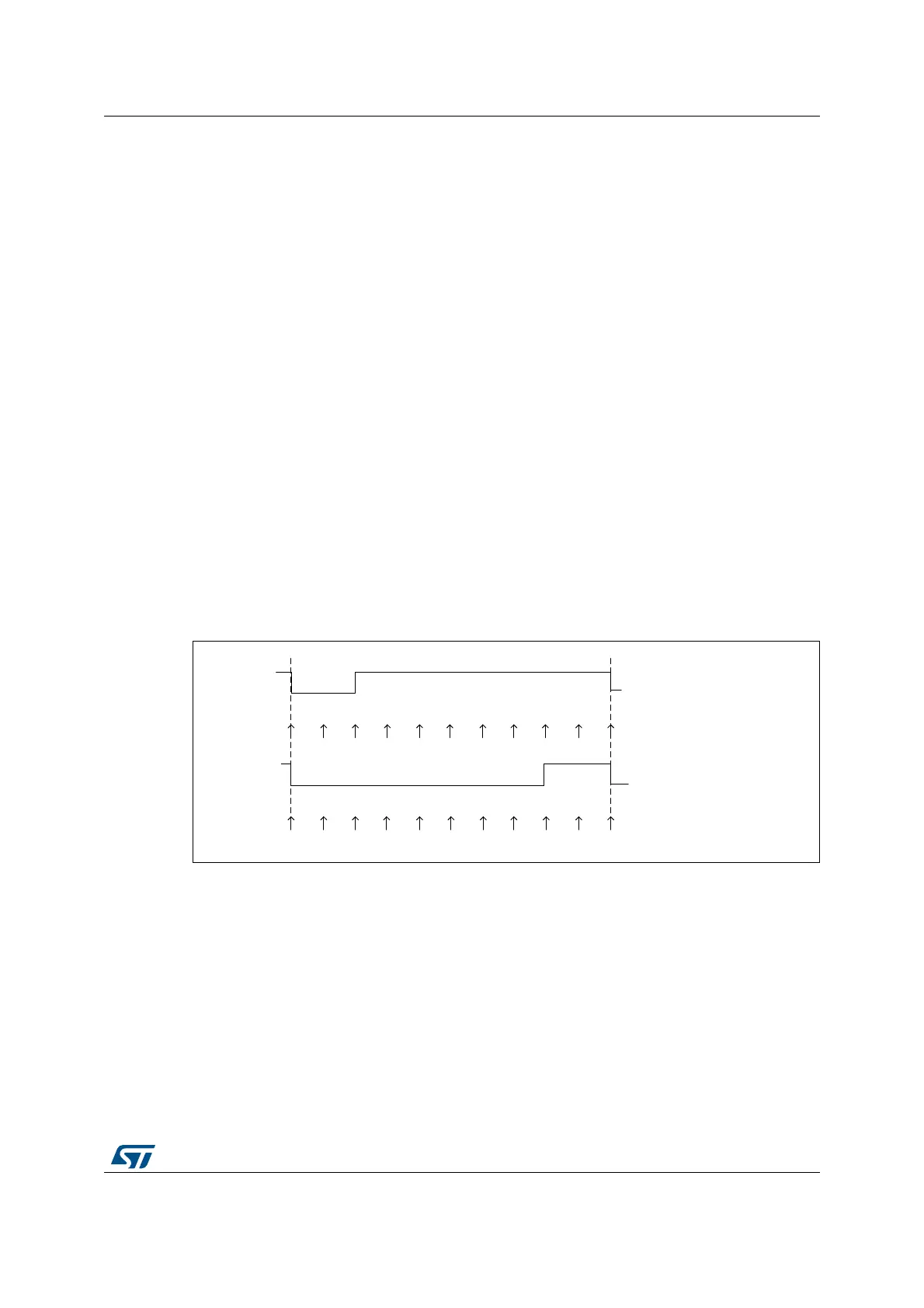

3.3.1 High speed bit format

One bit is generated with ten SWIM clock pulses.

The bit format is:

• 2 pulses at ‘0’ followed by 8 pulses at ‘1’ for ‘1’ value.

• 8 pulses at ‘0’ followed by 2 pulses at ‘1’ for ‘0’ value.

When the SWIM receives a data packet, it will decode:

• ‘1’ when the number of consecutive samples at ‘0’ is less or equal to 4.

• ‘0’ when the number of consecutive samples at ‘0’ is greater or equal to 5.

Figure 6. High speed bit format

Loading...

Loading...